## ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS

Paul R. Gray Paul J. Hurst Stephen H. Lewis Robert G. Meyer

# ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS

Fifth Edition

PAUL R. GRAY University of California, Berkeley

**PAUL J. HURST** *University of California, Davis*

**STEPHEN H. LEWIS** University of California, Davis

**ROBERT G. MEYER** *University of California, Berkeley*

New York / Chichester / Weinheim / Brisbane / Singapore / Toronto www.Techbooksyard.com

| PUBLISHER                      | Don Fowley                     |

|--------------------------------|--------------------------------|

| ACQUISITIONS EDITOR            | Daniel Sayre                   |

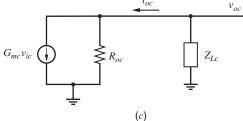

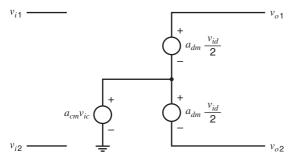

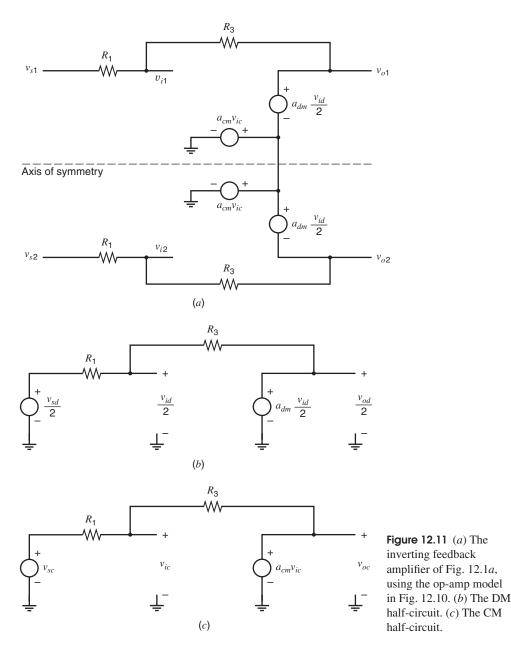

| SENIOR PRODUCTION EDITOR       | Valerie A. Vargas              |

| EXECUTIVE MARKETING MANAGER    | Christopher Ruel               |

| DESIGNER                       | Arthur Medina                  |

| PRODUCTION MANAGEMENT SERVICES | Elm Street Publishing Services |

| EDITORIAL ASSISTANT            | Carolyn Weisman                |

| MEDIA EDITOR                   | Lauren Sapira                  |

Cover courtesy of Chi Ho Law.

This book was set in 10/12 Times Roman by Thomson Digital and printed and bound by Hamilton Printing Company. The cover was printed by Phoenix Color, Inc.

This book was printed on acid-free paper.  $\otimes$

Copyright 2009 © John Wiley & Sons, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center Inc., 222 Rosewood Drive, Danvers, MA 01923, website www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030-5774, (201) 748-6011, fax (201) 748-6008, website http://www.wiley.com/go/permissions. To order books or for customer service please call 1-800-CALL-WILEY (255-5945).

http://www.wiley.com/college/gray

#### Library of Congress Cataloging-in-Publication Data

Analysis and design of analog integrated circuits / Paul R. Gray . . . [et al.]. — 5th ed. p. cm.

Includes bibliographical references and index.

ISBN 978-0-470-24599-6 (cloth: alk. paper)

1. Linear integrated circuits-Computer-aided design. 2. Metal oxide semiconductors-Computer-aided design. 3. Bipolar transistors-Computer-aided design.

I. Gray, Paul R., 1942TK7874.A588 2009

621.3815-dc21

08-043583

Printed in the United States of America

To Liz, Barbara, Robin, and Judy

# Preface

Since the publication of the first edition of this book, the field of analog integrated circuits has developed and matured. The initial groundwork was laid in bipolar technology, followed by a rapid evolution of MOS analog integrated circuits. Thirty years ago, CMOS technologies were fast enough to support applications only at audio frequencies. However, the continuing reduction of the minimum feature size in integrated-circuit (IC) technologies has greatly increased the maximum operating frequencies, and CMOS technologies have become fast enough for many new applications as a result. For example, the bandwidth in some video applications is about 4 MHz, requiring bipolar technologies as recently as about twenty-three years ago. Now, however, CMOS easily can accommodate the required bandwidth for video and is being used for radio-frequency applications. Today, bipolar integrated circuits are used in some applications that require very low noise, very wide bandwidth, or driving low-impedance loads.

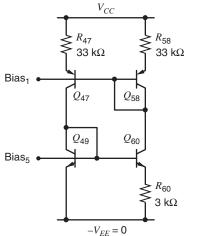

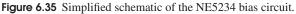

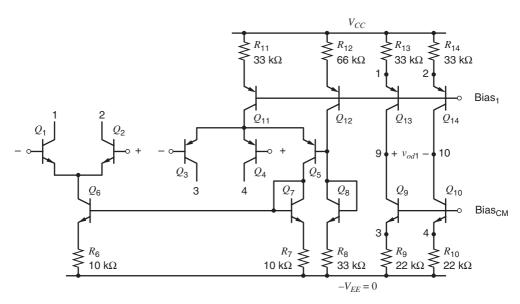

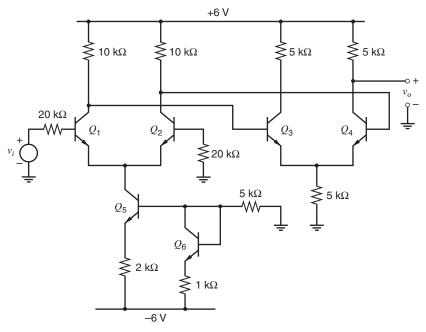

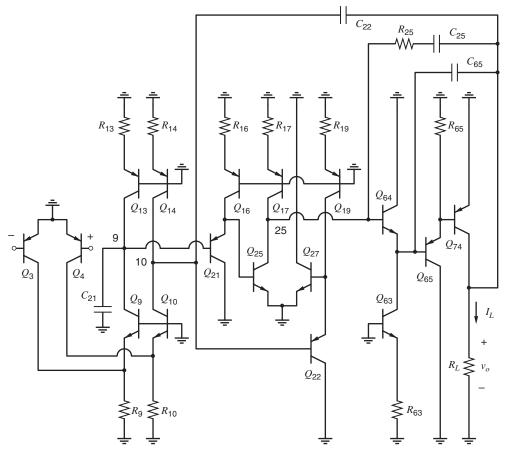

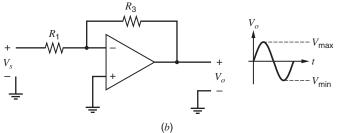

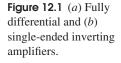

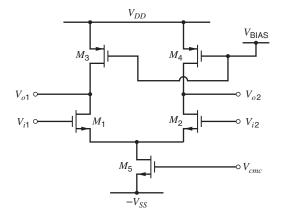

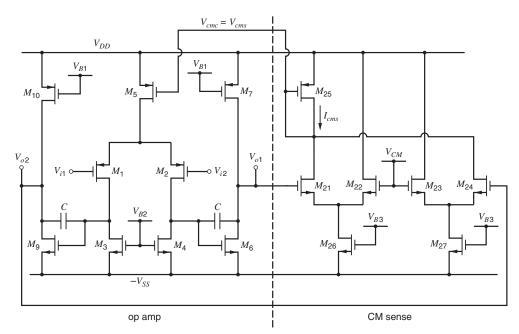

In this fifth edition, coverage of the bipolar 741 op amp has been replaced with a low-voltage bipolar op amp, the NE5234, with rail-to-rail common-mode input range and almost rail-to-rail output swing. Analysis of a fully differential CMOS folded-cascode operational amplifier (op amp) is now included in Chapter 12. The 560B phase-locked loop, which is no longer commercially available, has been deleted from Chapter 10.

The SPICE computer analysis program is now readily available to virtually all electrical engineering students and professionals, and we have included extensive use of SPICE in this edition, particularly as an integral part of many problems. We have used computer analysis as it is most commonly employed in the engineering design process—both as a more accurate check on hand calculations, and also as a tool to examine complex circuit behavior beyond the scope of hand analysis.

An in-depth look at SPICE as an indispensable tool for IC robust design can be found in The SPICE Book, 2nd ed., published by J. Wiley and Sons. This text contains many worked out circuit designs and verification examples linked to the multitude of analyses available in the most popular versions of SPICE. The SPICE Book conveys the role of simulation as an integral part of the design process, but not as a replacement for solid circuit-design knowledge.

This book is intended to be useful both as a text for students and as a reference book for practicing engineers. For class use, each chapter includes many worked problems; the problem sets at the end of each chapter illustrate the practical applications of the material in the text. All of the authors have extensive industrial experience in IC design and in the teaching of courses on this subject; this experience is reflected in the choice of text material and in the problem sets.

Although this book is concerned largely with the analysis and design of ICs, a considerable amount of material also is included on applications. In practice, these two subjects are closely linked, and a knowledge of both is essential for designers and users of ICs. The latter compose the larger group by far, and we believe that a working knowledge of IC design is a great advantage to an IC user. This is particularly apparent when the user must choose from among a number of competing designs to satisfy a particular need. An understanding of the IC structure is then useful in evaluating the relative desirability of the different designs under extremes of environment or in the presence of variations in supply voltage. In addition, the IC user is in a

much better position to interpret a manufacturer's data if he or she has a working knowledge of the internal operation of the integrated circuit.

The contents of this book stem largely from courses on analog integrated circuits given at the University of California at the Berkeley and Davis campuses. The courses are senior-level electives and first-year graduate courses. The book is structured so that it can be used as the basic text for a sequence of such courses. The more advanced material is found at the end of each chapter or in an appendix so that a first course in analog integrated circuits can omit this material without loss of continuity. An outline of each chapter is given below with suggestions for material to be covered in such a first course. It is assumed that the course consists of three hours of lecture per week over a fifteen-week semester and that the students have a working knowledge of Laplace transforms and frequency-domain circuit analysis. It is also assumed that the students have had an introductory course in electronics so that they are familiar with the principles of transistor operation and with the functioning of simple analog circuits. Unless otherwise stated, each chapter requires three to four lecture hours to cover.

Chapter 1 contains a summary of bipolar transistor and MOS transistor device physics. We suggest spending one week on selected topics from this chapter, with the choice of topics depending on the background of the students. The material of Chapters 1 and 2 is quite important in IC design because there is significant interaction between circuit and device design, as will be seen in later chapters. A thorough understanding of the influence of device fabrication on device characteristics is essential.

Chapter 2 is concerned with the technology of IC fabrication and is largely descriptive. One lecture on this material should suffice if the students are assigned the chapter to read.

Chapter 3 deals with the characteristics of elementary transistor connections. The material on one-transistor amplifiers should be a review for students at the senior and graduate levels and can be assigned as reading. The section on two-transistor amplifiers can be covered in about three hours, with greatest emphasis on differential pairs. The material on device mismatch effects in differential amplifiers can be covered to the extent that time allows.

In Chapter 4, the important topics of current mirrors and active loads are considered. These configurations are basic building blocks in modern analog IC design, and this material should be covered in full, with the exception of the material on band-gap references and the material in the appendices.

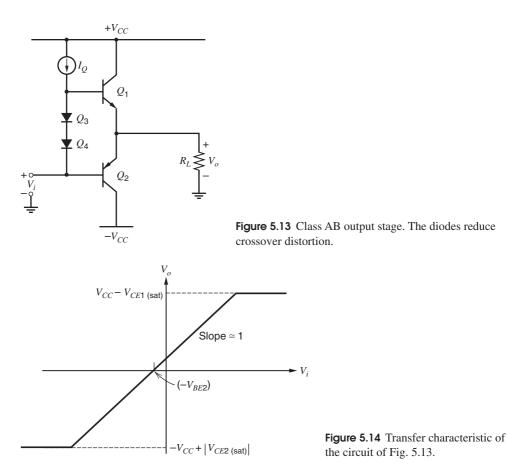

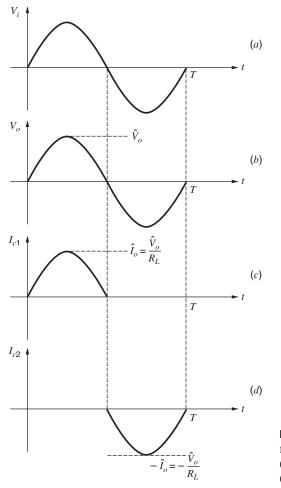

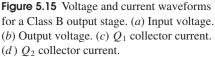

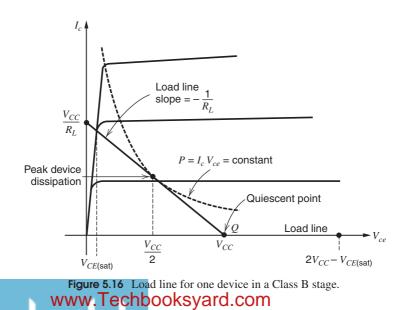

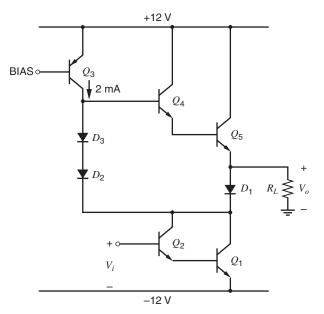

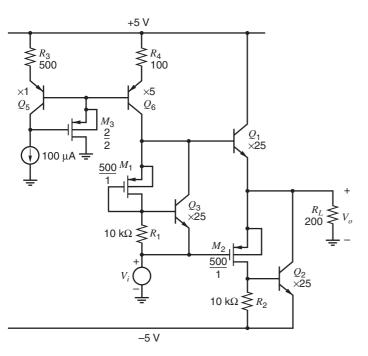

Chapter 5 is concerned with output stages and methods of delivering output power to a load. Integrated-circuit realizations of Class A, Class B, and Class AB output stages are described, as well as methods of output-stage protection. A selection of topics from this chapter should be covered.

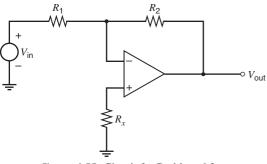

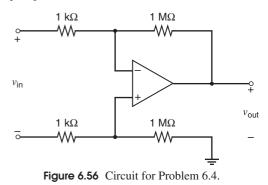

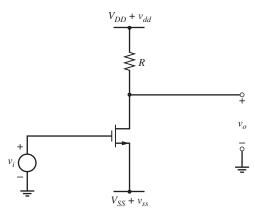

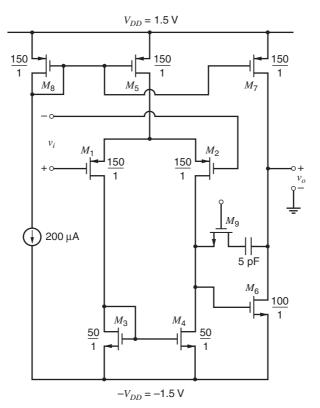

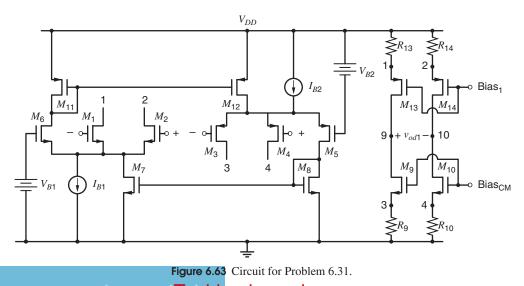

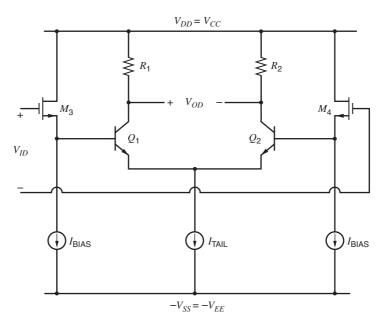

Chapter 6 deals with the design of operational amplifiers (op amps). Illustrative examples of dc and ac analysis in both MOS and bipolar op amps are performed in detail, and the limitations of the basic op amps are described. The design of op amps with improved characteristics in both MOS and bipolar technologies are considered. This key chapter on amplifier design requires at least six hours.

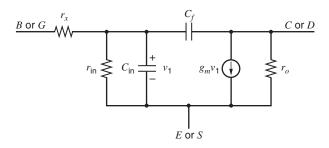

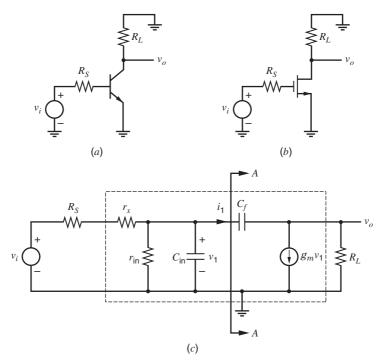

In Chapter 7, the frequency response of amplifiers is considered. The zero-value time-constant technique is introduced for the calculations of the –3-dB frequency of complex circuits. The material of this chapter should be considered in full.

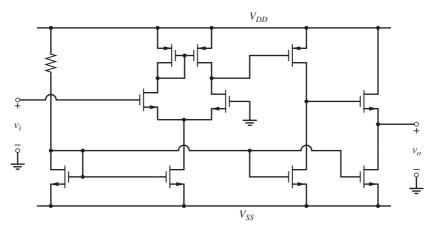

Chapter 8 describes the analysis of feedback circuits. Two different types of analysis are presented: two-port and return-ratio analyses. Either approach should be covered in full with the section on voltage regulators assigned as reading.

Chapter 9 deals with the frequency response and stability of feedback circuits and should be covered up to the section on root locus. Time may not permit a detailed discussion of root locus, but some introduction to this topic can be given.

In a fifteen-week semester, coverage of the above material leaves about two weeks for Chapters 10, 11, and 12. A selection of topics from these chapters can be chosen as follows. Chapter 10 deals with nonlinear analog circuits and portions of this chapter up to Section 10.2 could be covered in a first course. Chapter 11 is a comprehensive treatment of noise in integrated circuits and material up to and including Section 11.4 is suitable. Chapter 12 describes fully differential operational amplifiers and common-mode feedback and may be best suited for a second course.

We are grateful to the following colleagues for their suggestions for and/or evaluation of this book: R. Jacob Baker, Bernhard E. Boser, A. Paul Brokaw, Iwen Chao, John N. Churchill, David W. Cline, Kenneth C. Dyer, Ozan E. Erdoğan, John W. Fattaruso, Weinan Gao, Edwin W. Greeneich, Alex Gros-Balthazard, Tünde Gyurics, Ward J. Helms, Kaveh Hosseini, Timothy H. Hu, Shafiq M. Jamal, John P. Keane, Haideh Khorramabadi, Pak Kim Lau, Thomas W. Matthews, Krishnaswamy Nagaraj, Khalil Najafi, Borivoje Nikolić, Keith O'Donoghue, Robert A. Pease, Lawrence T. Pileggi, Edgar Sánchez-Sinencio, Bang-Sup Song, Richard R. Spencer, Eric J. Swanson, Andrew Y. J. Szeto, Yannis P. Tsividis, Srikanth Vaidianathan, T. R. Viswanathan, Chorng-Kuang Wang, Dong Wang, and Mo Maggie Zhang. We are also grateful to Darrel Akers, Mu Jane Lee, Lakshmi Rao, Nattapol Sitthimahachaikul, Haoyue Wang, and Mo Maggie Zhang for help with proofreading, and to Chi Ho Law for allowing us to use on the cover of this book a die photograph of an integrated circuit he designed. Finally, we would like to thank the staffs at Wiley and Elm Street Publishing Services for their efforts in producing this edition.

The material in this book has been greatly influenced by our association with the late Donald O. Pederson, and we acknowledge his contributions.

Berkeley and Davis, CA, 2008

Paul R. Gray Paul J. Hurst Stephen H. Lewis Robert G. Meyer

# Contents

## CHAPTER 1 Models for Integrated-Circuit Active Devices 1

- 1.1 Introduction 1

- 1.2 Depletion Region of a *pn* Junction 1

- 1.2.1 Depletion-Region Capacitance 5

- 1.2.2 Junction Breakdown 6

- 1.3 Large-Signal Behavior of Bipolar Transistors 8

- 1.3.1 Large-Signal Models in the Forward-Active Region 8

- 1.3.2 Effects of Collector Voltage on Large-Signal Characteristics in the Forward-Active Region 14

- 1.3.3 Saturation and Inverse-Active Regions 16

- 1.3.4 Transistor Breakdown Voltages 20

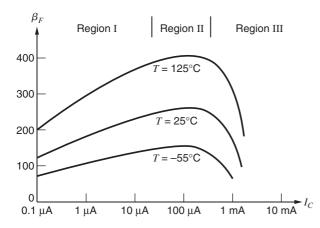

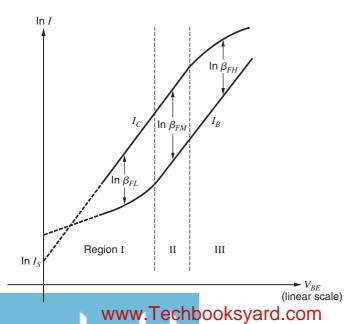

- 1.3.5 Dependence of Transistor Current Gain  $\beta_F$  on Operating Conditions 23

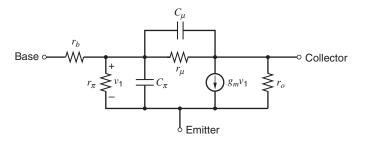

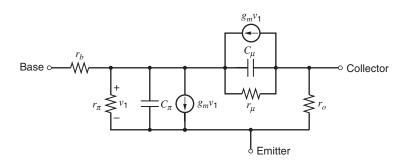

- 1.4 Small-Signal Models of Bipolar Transistors 25

- 1.4.1 Transconductance 26

- 1.4.2 Base-Charging Capacitance 27

- 1.4.3 Input Resistance 28

- 1.4.4 Output Resistance 29

- 1.4.5 Basic Small-Signal Model of the Bipolar Transistor 30

- 1.4.6 Collector-Base Resistance 30

- 1.4.7 Parasitic Elements in the Small-Signal Model 31

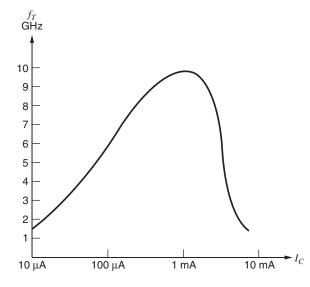

- 1.4.8 Specification of Transistor Frequency Response 34

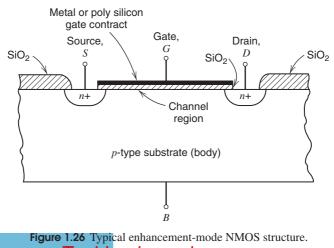

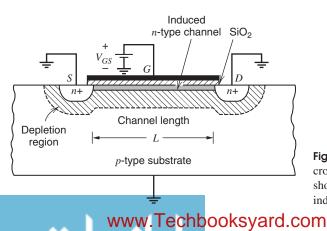

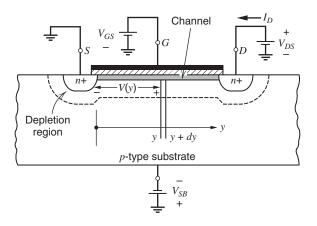

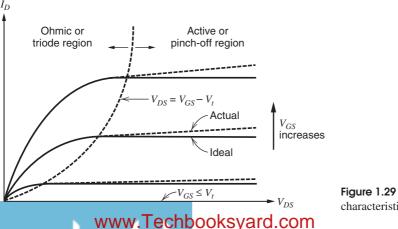

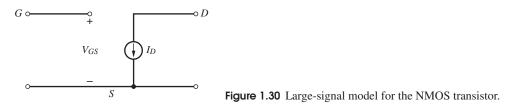

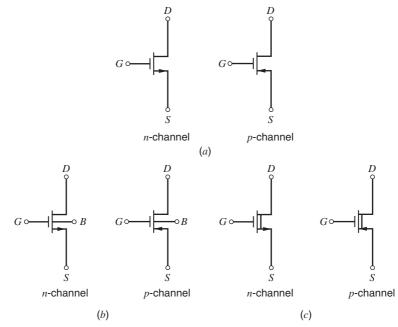

- Large-Signal Behavior of Metal-Oxide-Semiconductor Field-Effect Transistors 38

- 1.5.1 Transfer Characteristics of MOS Devices 38

- 1.5.2 Comparison of Operating Regions of Bipolar and MOS Transistors 45

- 1.5.3 Decomposition of Gate-Source Voltage 47

- 1.5.4 Threshold Temperature Dependence 47

- 1.5.5 MOS Device Voltage Limitations 48

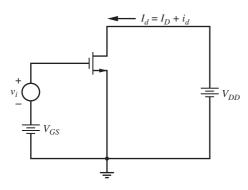

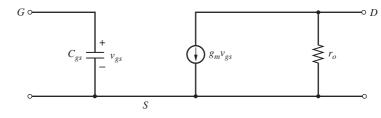

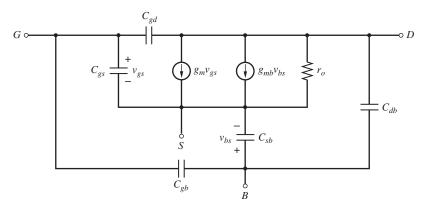

- 1.6 Small-Signal Models of MOS Transistors 49

- 1.6.1 Transconductance 50

- 1.6.2 Intrinsic Gate-Source and Gate-Drain Capacitance 51

- 1.6.3 Input Resistance 52

- 1.6.4 Output Resistance 52

- 1.6.5 Basic Small-Signal Model of the MOS Transistor 52

- 1.6.6 Body Transconductance 53

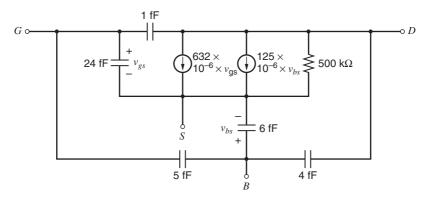

- 1.6.7 Parasitic Elements in the Small-Signal Model 54

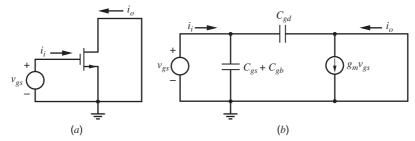

- 1.6.8 MOS Transistor Frequency Response 55

- Short-Channel Effects in MOS Transistors 59

- 1.7.1 Velocity Saturation from the Horizontal Field 59

- 1.7.2 Transconductance and Transition Frequency 63

- 1.7.3 Mobility Degradation from the Vertical Field 65

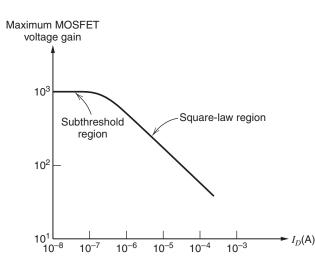

- 1.8 Weak Inversion in MOS Transistors 65

- 1.8.1 Drain Current in Weak Inversion 66

- 1.8.2 Transconductance and Transition Frequency in Weak Inversion 69

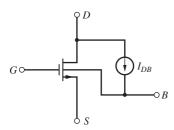

- 1.9 Substrate Current Flow in MOS Transistors 71

- A.1.1 Summary of Active-Device Parameters 73

## CHAPTER 2 Bipolar, MOS, and BiCMOS Integrated-Circuit Technology 78

- 2.1 Introduction 78

- 2.2 Basic Processes in Integrated-Circuit Fabrication 79

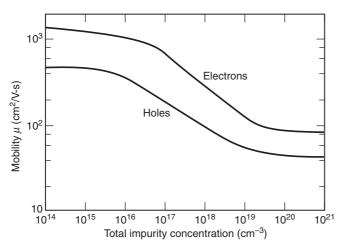

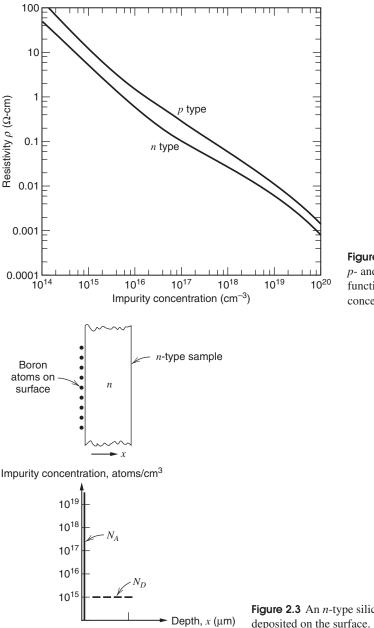

- 2.2.1 Electrical Resistivity of Silicon 79

- 2.2.2 Solid-State Diffusion 80

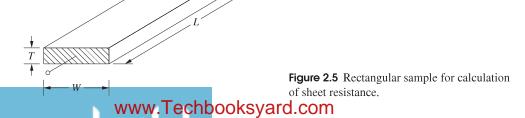

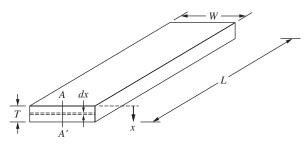

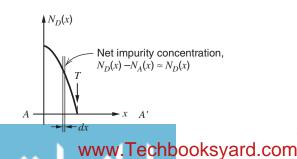

- 2.2.3 Electrical Properties of Diffused Layers 82

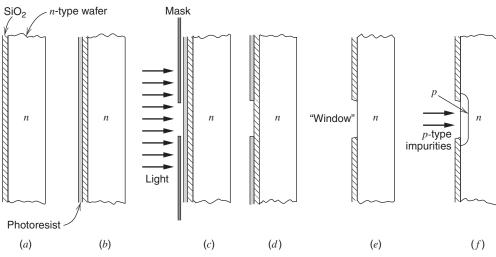

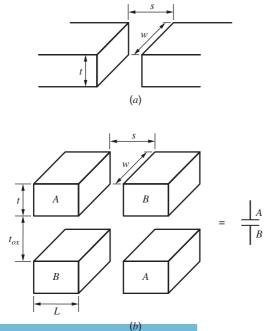

- 2.2.4 Photolithography 84

- 2.2.5 Epitaxial Growth 86

- 2.2.6 Ion Implantation 87

- 2.2.7 Local Oxidation 87

- 2.2.8 Polysilicon Deposition 87

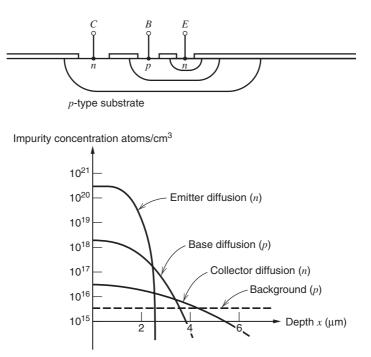

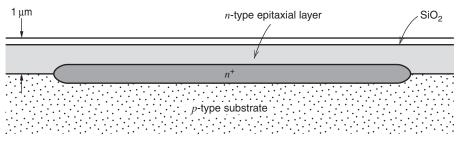

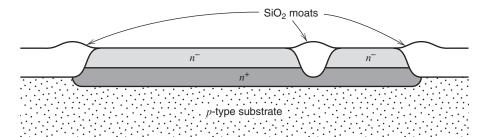

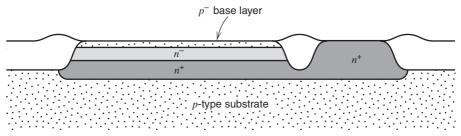

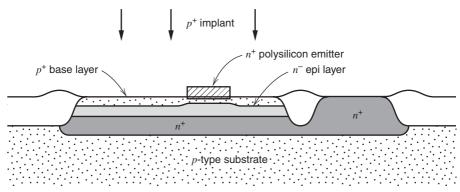

- 2.3 High-Voltage Bipolar Integrated-Circuit Fabrication 88

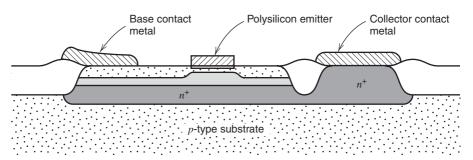

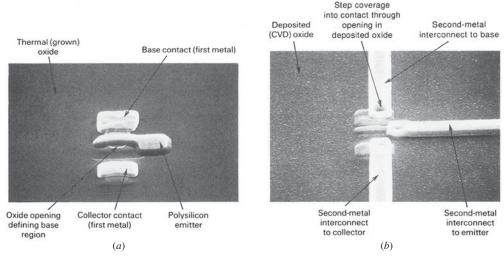

- 2.4 Advanced Bipolar Integrated-Circuit Fabrication 92

- 2.5 Active Devices in Bipolar Analog Integrated Circuits 95

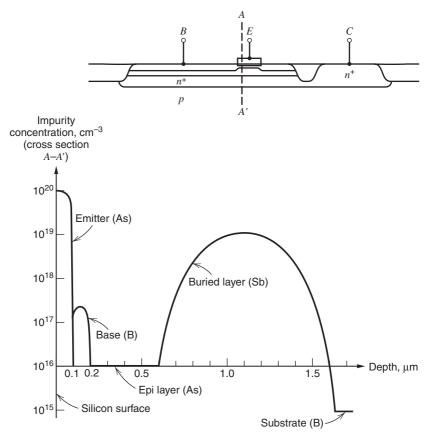

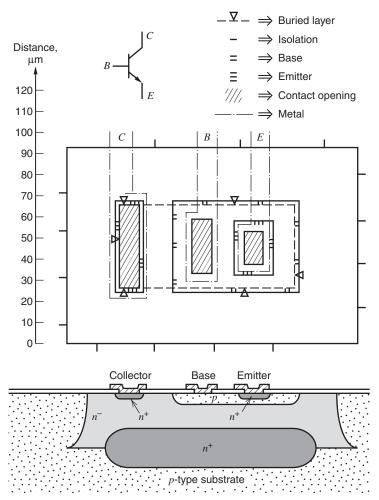

- 2.5.1 Integrated-Circuit *npn* Transistors 96

- 2.5.2 Integrated-Circuit *pnp* Transistors 107

- 2.6 Passive Components in Bipolar Integrated Circuits 115

- 2.6.1 Diffused Resistors 115

- 2.6.2 Epitaxial and Epitaxial Pinch Resistors 119

- 2.6.3 Integrated-Circuit Capacitors 120

- 2.6.4 Zener Diodes 121

- 2.6.5 Junction Diodes 122

- 2.7 Modifications to the Basic Bipolar Process 123

- 2.7.1 Dielectric Isolation 123

- 2.7.2 Compatible Processing for High-Performance Active Devices 124

- 2.7.3 High-Performance Passive Components 127

- 2.8 MOS Integrated-Circuit Fabrication 127

- 2.9 Active Devices in MOS Integrated Circuits 131

- 2.9.1 *n*-Channel Transistors 131

- 2.9.2 *p*-Channel Transistors 144

- 2.9.3 Depletion Devices 144

- 2.9.4 Bipolar Transistors 145

- 2.10 Passive Components in MOS Technology 146

- 2.10.1 Resistors 146

- 2.10.2 Capacitors in MOS Technology 148

- 2.10.3 Latchup in CMOS Technology 151

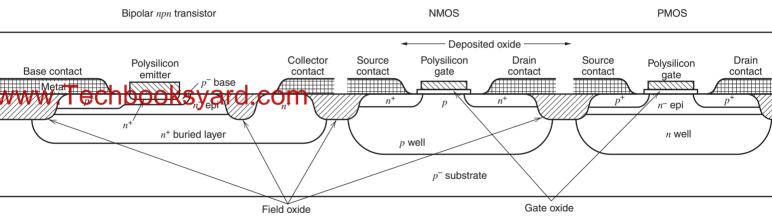

- 2.11 BiCMOS Technology 152

- 2.12 Heterojunction Bipolar Transistors 153

- 2.13 Interconnect Delay 156

- 2.14 Economics of Integrated-Circuit Fabrication 156

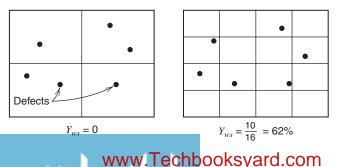

- 2.14.1 Yield Considerations in Integrated-Circuit Fabrication 157

- 2.14.2 Cost Considerations in Integrated-Circuit Fabrication 159

- A.2.1 SPICE Model-Parameter Files 162

#### CHAPTER 3

## Single-Transistor and Multiple-Transistor Amplifiers 169

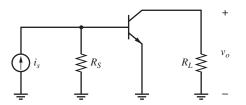

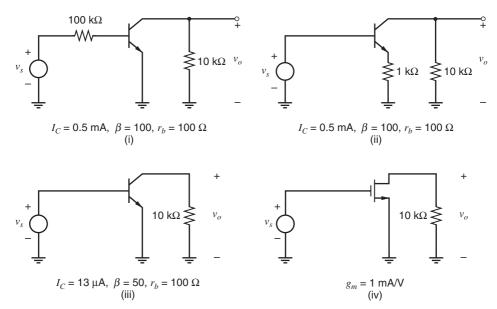

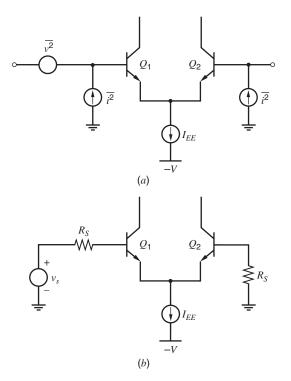

- 3.1 Device Model Selection for Approximate Analysis of Analog Circuits 170

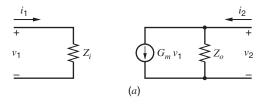

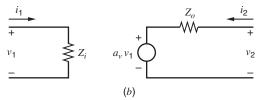

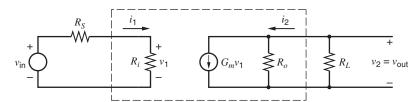

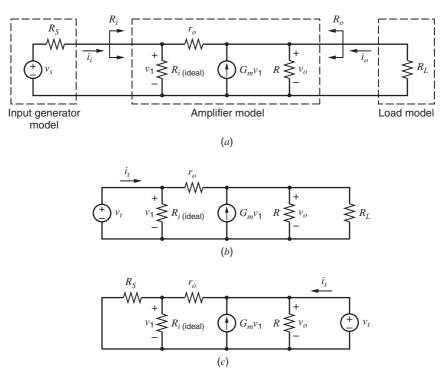

- 3.2 Two-Port Modeling of Amplifiers 171

- 3.3 Basic Single-Transistor Amplifier Stages 173

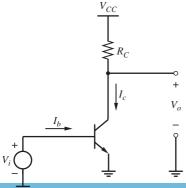

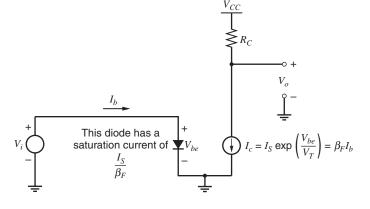

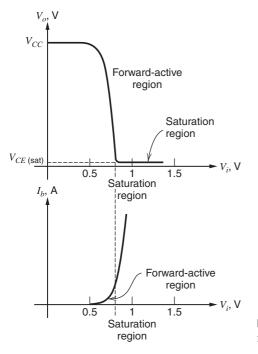

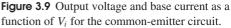

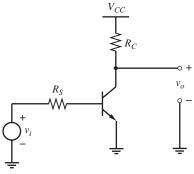

- 3.3.1 Common-Emitter Configuration 174

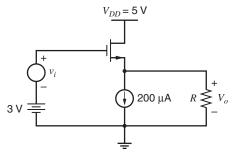

- 3.3.2 Common-Source Configuration 178

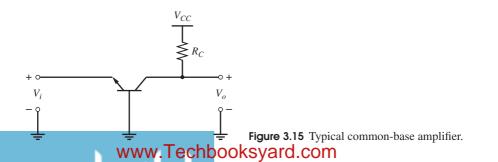

- 3.3.3 Common-Base Configuration 182

- 3.3.4 Common-Gate Configuration 185

- 3.3.5 Common-Base and Common-Gate Configurations with Finite  $r_0$  187

- 3.3.5.1 Common-Base and Common-Gate Input Resistance 187

- 3.3.5.2 Common-Base and Common-Gate Output Resistance 189

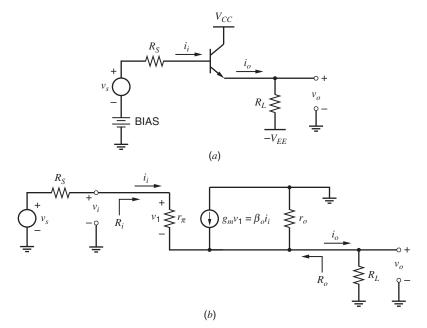

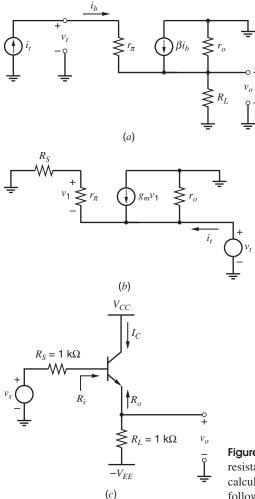

- 3.3.6 Common-Collector Configuration (Emitter Follower) 191

- 3.3.7 Common-Drain Configuration (Source Follower) 194

- 3.3.8 Common-Emitter Amplifier with Emitter Degeneration 196

- 3.3.9 Common-Source Amplifier with Source Degeneration 199

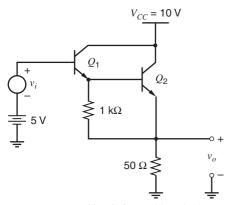

- 3.4 Multiple-Transistor Amplifier Stages 201

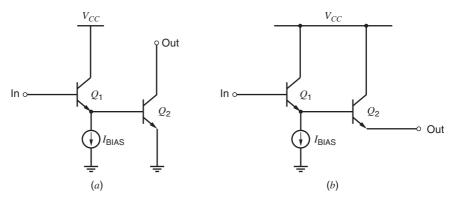

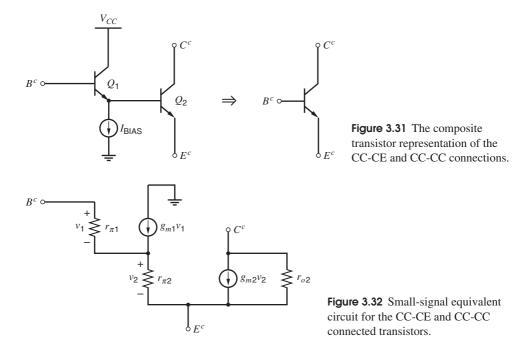

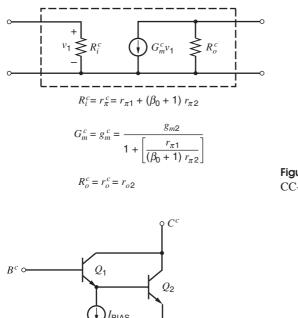

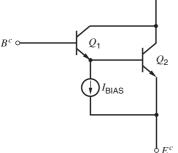

- 3.4.1 The CC-CE, CC-CC, and Darlington Configurations 201

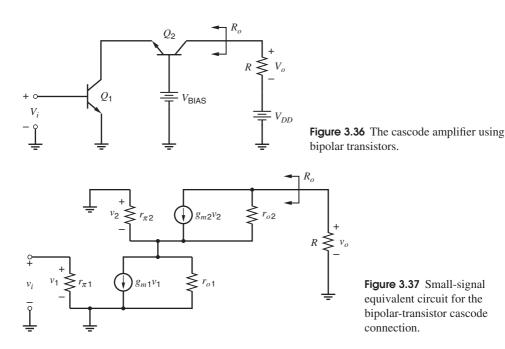

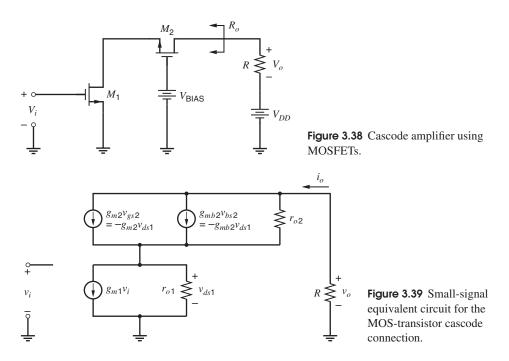

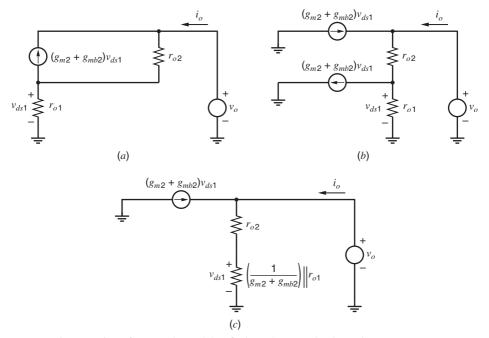

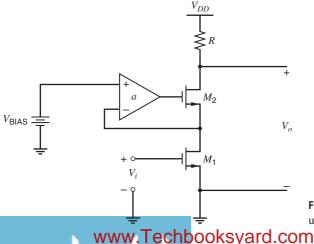

- 3.4.2The Cascode Configuration2053.4.2.1The Bipolar Cascode2053.4.2.2The MOS Cascode207

- 3.4.3 The Active Cascode 210

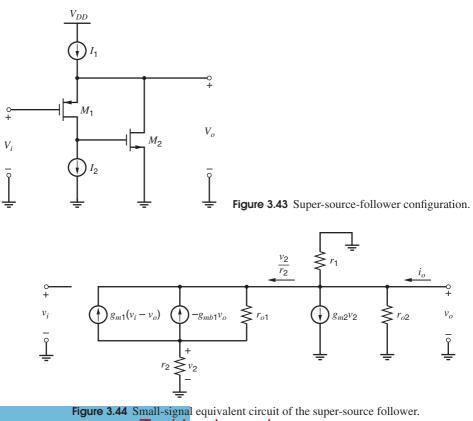

- 3.4.4 The Super Source Follower 212

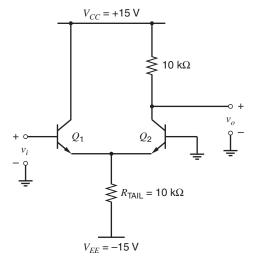

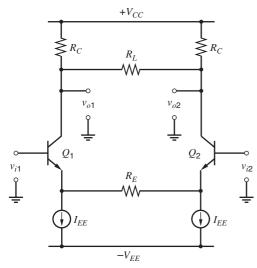

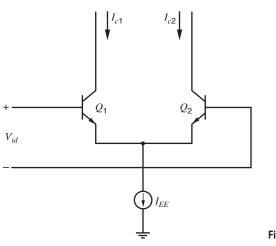

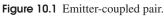

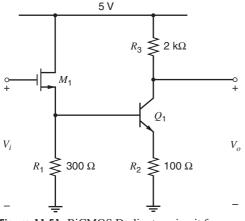

- 3.5 Differential Pairs 214

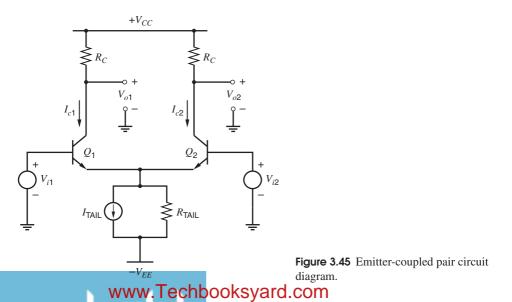

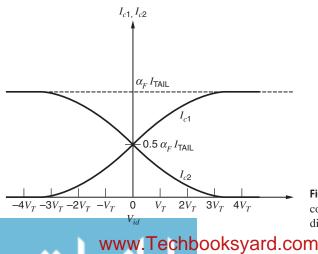

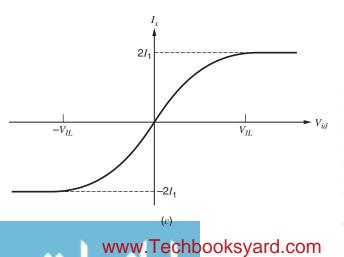

- 3.5.1 The dc Transfer Characteristic of an Emitter-Coupled Pair 214

- 3.5.2 The dc Transfer Characteristic with Emitter Degeneration 216

- 3.5.3 The dc Transfer Characteristic of a Source-Coupled Pair 217

- 3.5.4 Introduction to the Small-Signal Analysis of Differential Amplifiers 220

- 3.5.5 Small-Signal Characteristics of Balanced Differential Amplifiers 223

- 3.5.6 Device Mismatch Effects in Differential Amplifiers 229

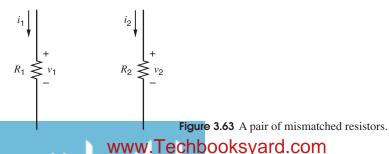

- 3.5.6.1 Input Offset Voltage and Current 230

- 3.5.6.2 Input Offset Voltage of the Emitter-Coupled Pair 230

- 3.5.6.3 Offset Voltage of the Emitter-Coupled Pair: Approximate Analysis 231

- 3.5.6.4 Offset Voltage Drift in the Emitter-Coupled Pair 233

- 3.5.6.5 Input Offset Current of the Emitter-Coupled Pair 233

- 3.5.6.6 Input Offset Voltage of the Source-Coupled Pair 234

- 3.5.6.7 Offset Voltage of the Source-Coupled Pair: Approximate Analysis 235

- 3.5.6.8 Offset Voltage Drift in the Source-Coupled Pair 236

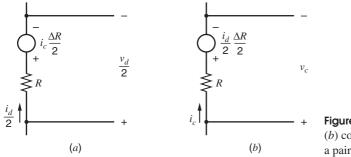

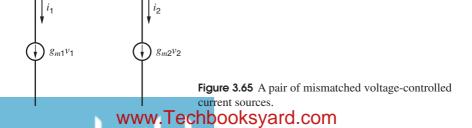

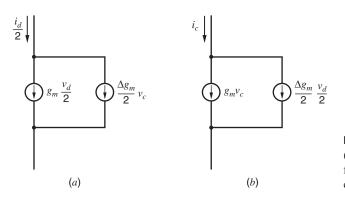

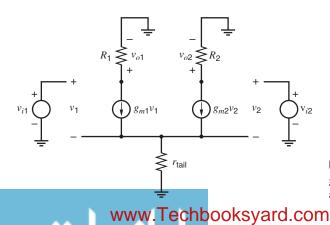

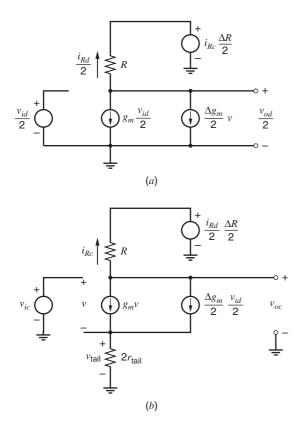

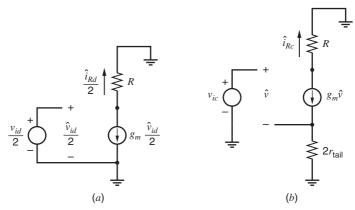

3.5.6.9 Small-Signal Characteristics of Unbalanced Differential Amplifiers 237

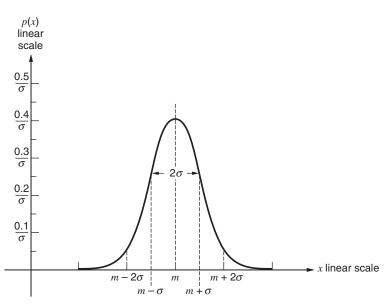

- A.3.1 Elementary Statistics and the Gaussian Distribution 244

## CHAPTER 4

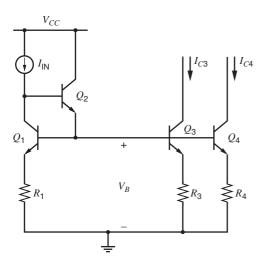

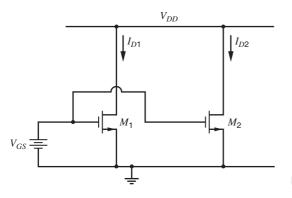

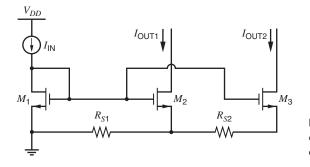

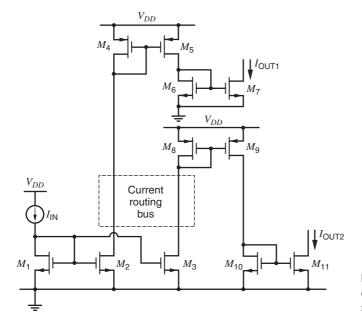

## Current Mirrors, Active Loads, and References 251

- 4.1 Introduction 251

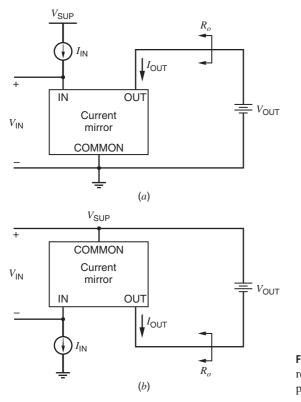

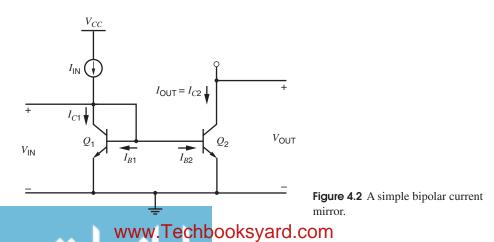

- 4.2 Current Mirrors 251

- 4.2.1 General Properties 251

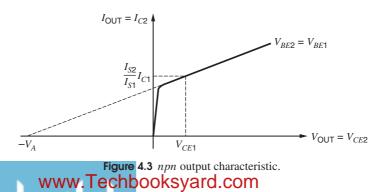

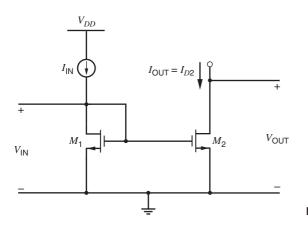

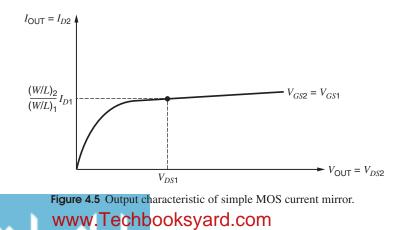

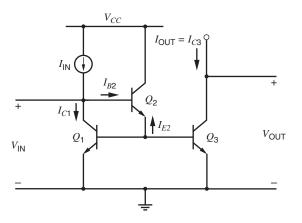

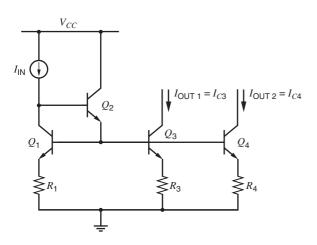

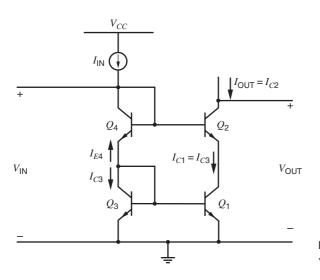

- 4.2.2 Simple Current Mirror 253 4.2.2.1 Bipolar 253 4.2.2.2 MOS 255

- 4.2.3 Simple Current Mirror with Beta Helper 258

4.2.3.1 Bipolar 258

4.2.3.2 MOS 260

- 4.2.4 Simple Current Mirror with Degeneration 260 4.2.4.1 Bipolar 260 4.2.4.2 MOS 261

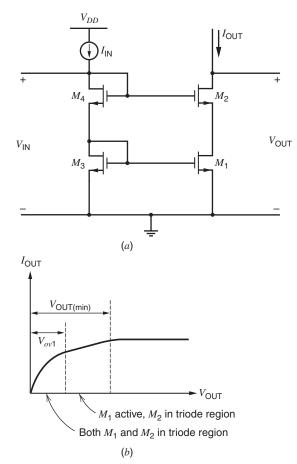

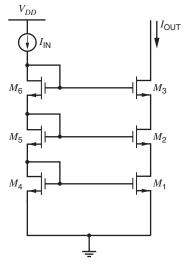

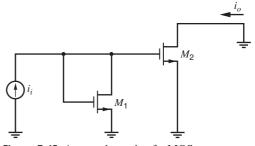

- 4.2.5 Cascode Current Mirror 261 4.2.5.1 Bipolar 261 4.2.5.2 MOS 264

- 4.2.6 Wilson Current Mirror 272 4.2.6.1 Bipolar 272 4.2.6.2 MOS 275

- 4.3 Active Loads 276

- 4.3.1 Motivation 276

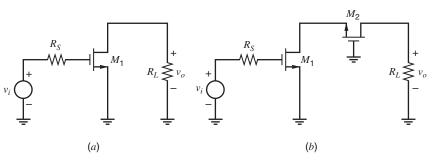

- 4.3.2 Common-Emitter–Common-Source Amplifier with Complementary Load 277

- 4.3.3 Common-Emitter–Common-Source Amplifier with Depletion Load 280

- 4.3.4 Common-Emitter–Common-Source Amplifier with Diode-Connected Load 282

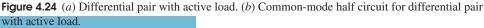

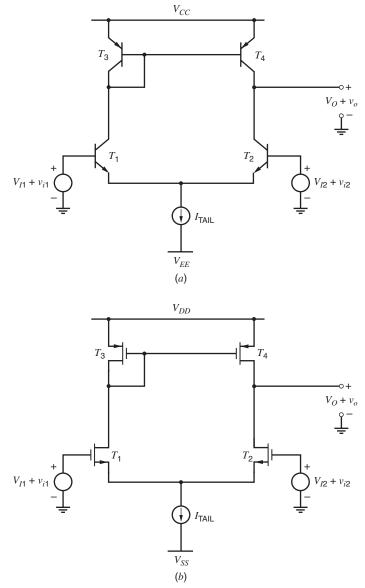

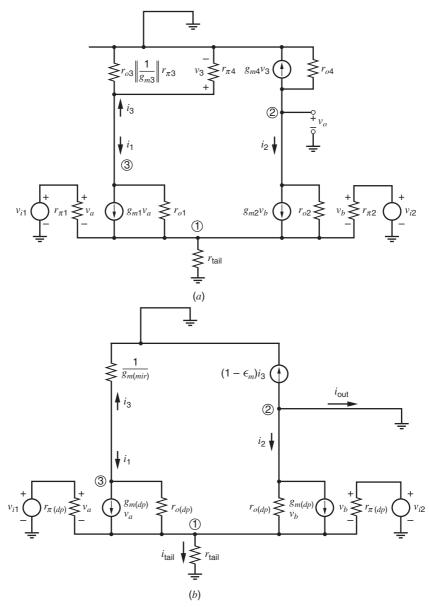

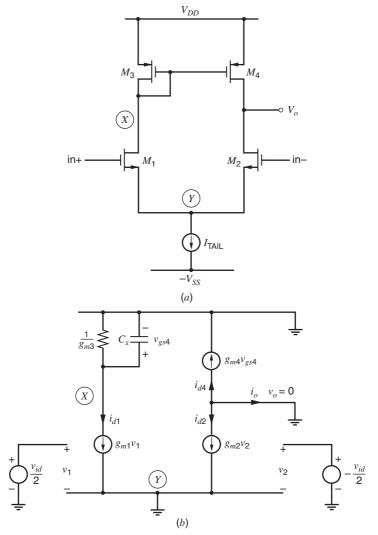

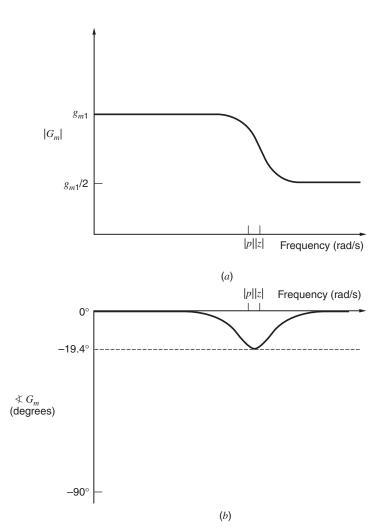

- 4.3.5 Differential Pair with Current-Mirror Load 285

- 4.3.5.1 Large-Signal Analysis 285

- 4.3.5.2 Small-Signal Analysis 286

- 4.3.5.3 Common-Mode Rejection Ratio 291

#### x Contents

- 4.4 Voltage and Current References 297

- 4.4.1 Low-Current Biasing 297

- 4.4.1.1 Bipolar Widlar Current Source 297

- 4.4.1.2 MOS Widlar Current Source 300

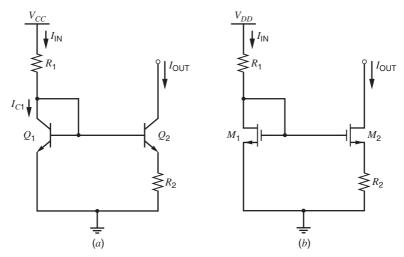

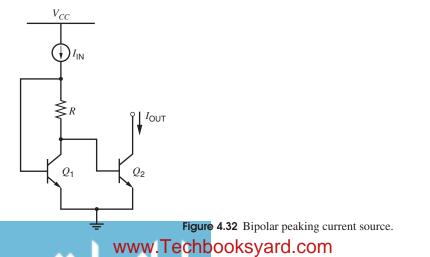

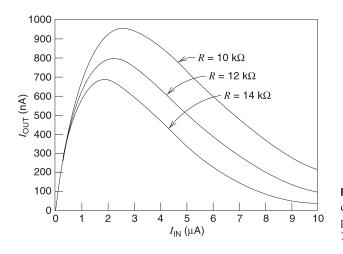

- 4.4.1.3 Bipolar Peaking Current Source 301

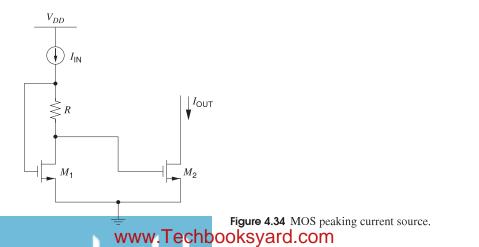

- 4.4.1.4 MOS Peaking Current Source 302

- 4.4.2 Supply-Insensitive Biasing 303

- 4.4.2.1 Widlar Current Sources 304

- 4.4.2.2 Current Sources Using Other Voltage Standards 305

- 4.4.2.3 Self-Biasing 307

- 4.4.3 Temperature-Insensitive Biasing 315

- 4.4.3.1 Band-Gap-Referenced Bias Circuits in Bipolar Technology 315

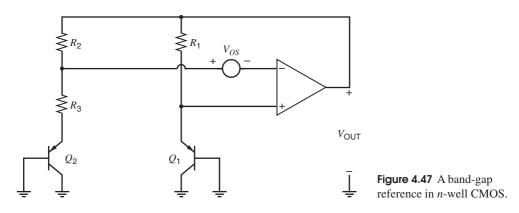

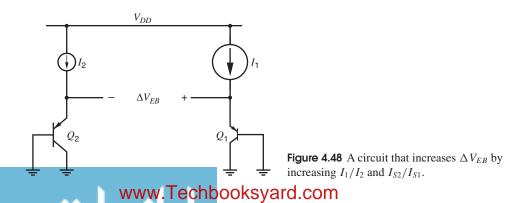

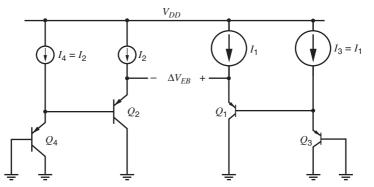

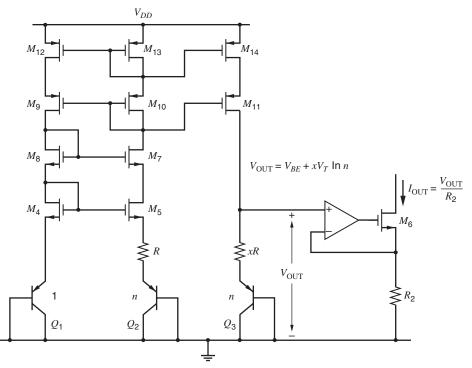

- 4.4.3.2 Band-Gap-Referenced Bias Circuits in CMOS Technology 321

- A.4.1 Matching Considerations in Current Mirrors 325 A.4.1.1 Bipolar 325 A.4.1.2 MOS 328

- A.4.2 Input Offset Voltage of Differential Pair with Active Load 330 A.4.2.1 Bipolar 330 A.4.2.2 MOS 332

## CHAPTER 5 Output Stages 341

- 5.1 Introduction 341

- 5.2 The Emitter Follower as an Output Stage 341

- 5.2.1 Transfer Characteristics of the Emitter-Follower 341

- 5.2.2 Power Output and Efficiency 344

- 5.2.3 Emitter-Follower Drive Requirements 351

- 5.2.4 Small-Signal Properties of the Emitter Follower 352

- 5.3 The Source Follower as an Output Stage 353

- 5.3.1 Transfer Characteristics of the Source Follower 353

- 5.3.2 Distortion in the Source Follower 355

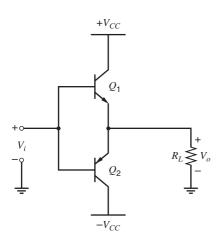

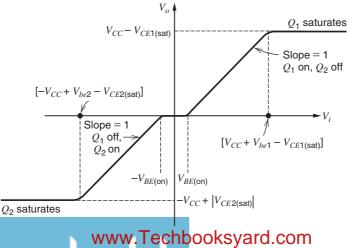

- 5.4 Class B Push–Pull Output Stage 359

- 5.4.1 Transfer Characteristic of the Class B Stage 360

- 5.4.2 Power Output and Efficiency of the Class B Stage 362

- 5.4.3 Practical Realizations of Class B Complementary Output Stages 366

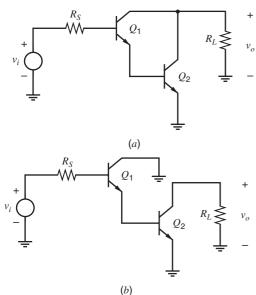

- 5.4.4 All-npn Class B Output Stage 373

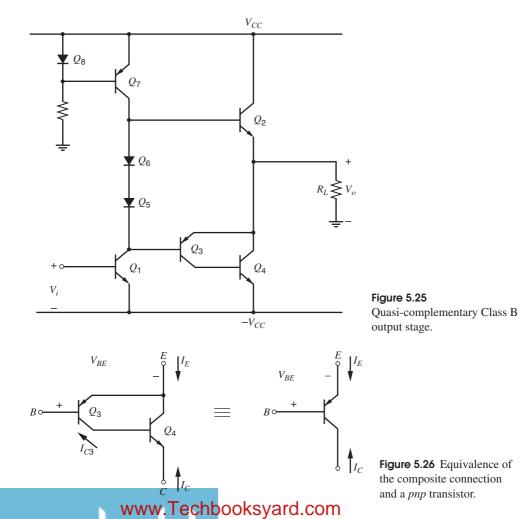

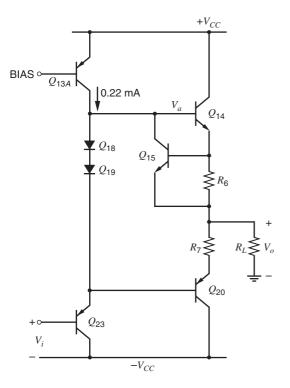

- 5.4.5 Quasi-Complementary Output Stages 376

- 5.4.6 Overload Protection 377

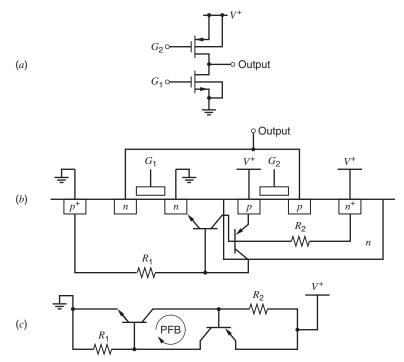

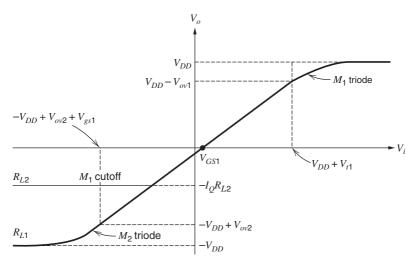

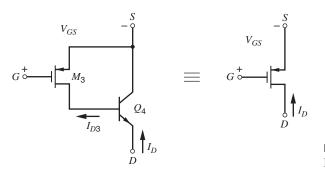

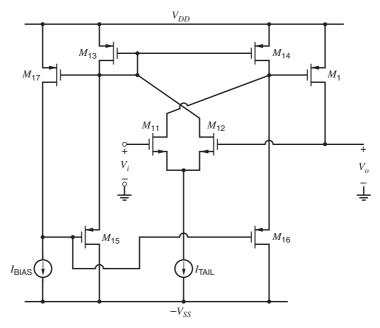

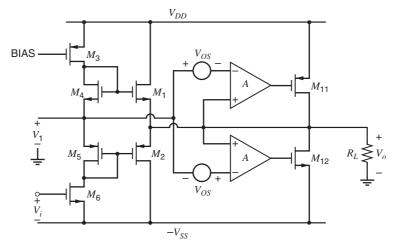

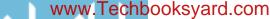

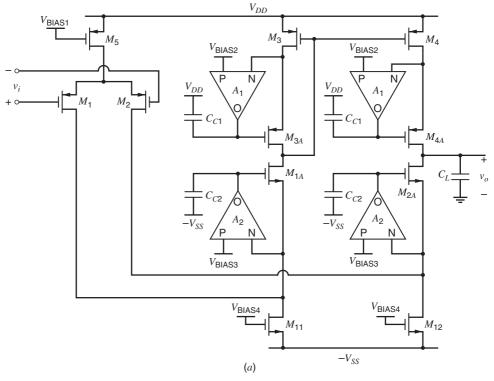

- 5.5 CMOS Class AB Output Stages 379

- 5.5.1 Common-Drain Configuration 380

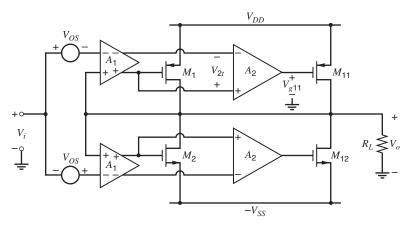

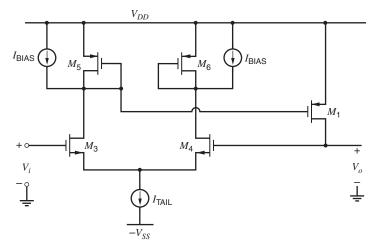

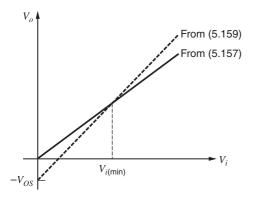

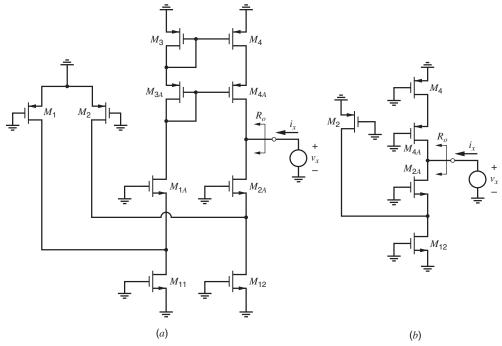

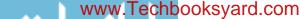

- 5.5.2 Common-Source Configuration with Error Amplifiers 381

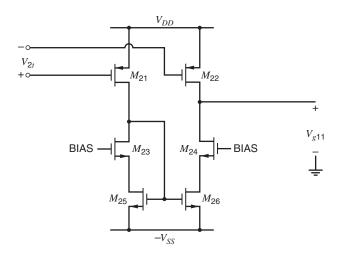

- 5.5.3 Alternative Configurations 388

- 5.5.3.1 Combined Common-Drain Common-Source Configuration 388

- 5.5.3.2 Combined Common-Drain Common-Source Configuration with High Swing 390

- 5.5.3.3 Parallel Common-Source Configuration 390

## CHAPTER 6

## Operational Amplifiers with Single-Ended Outputs 400

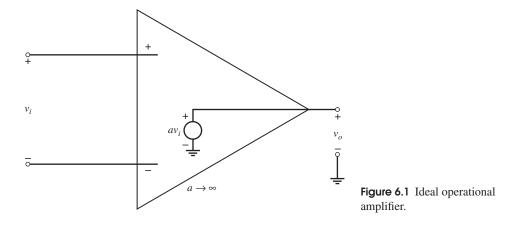

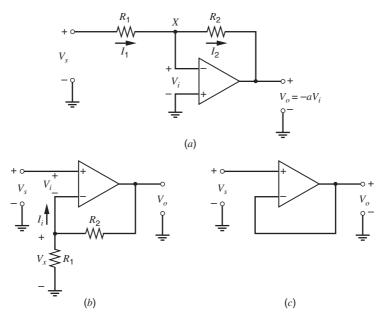

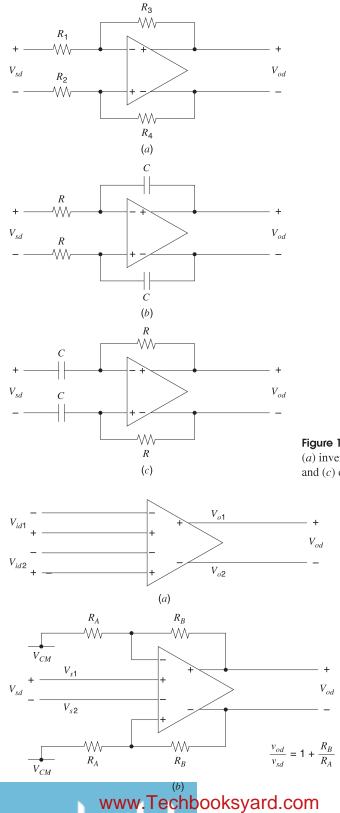

- 6.1 Applications of Operational Amplifiers 401

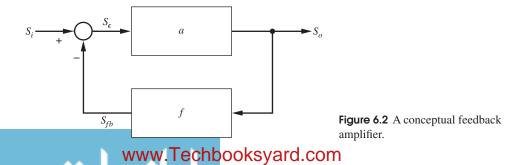

- 6.1.1 Basic Feedback Concepts 401

- 6.1.2 Inverting Amplifier 402

- 6.1.3 Noninverting Amplifier 404

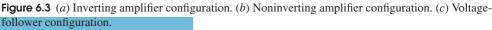

- 6.1.4 Differential Amplifier 404

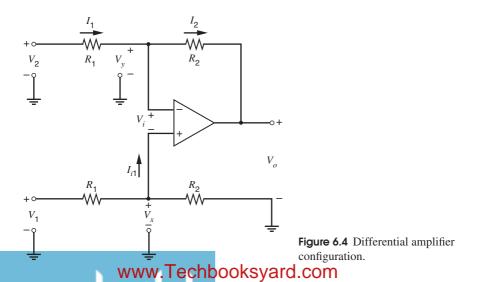

- 6.1.5 Nonlinear Analog Operations 405

- 6.1.6 Integrator, Differentiator 406

- 6.1.7 Internal Amplifiers 407

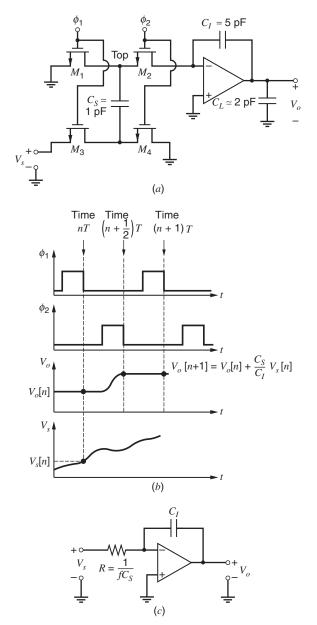

- 6.1.7.1 Switched-Capacitor Amplifier 407

- 6.1.7.2 Switched-Capacitor Integrator 412

- 6.2 Deviations from Ideality in Real Operational Amplifiers 415

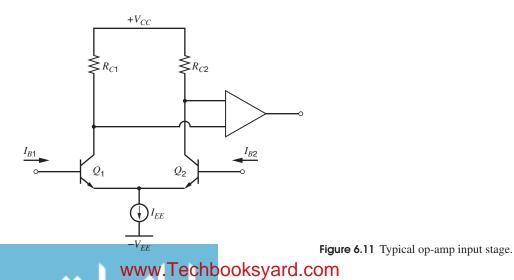

- 6.2.1 Input Bias Current 415

- 6.2.2 Input Offset Current 416

- 6.2.3 Input Offset Voltage 416

- 6.2.4 Common-Mode Input Range 416

- 6.2.5 Common-Mode Rejection Ratio (CMRR) 417

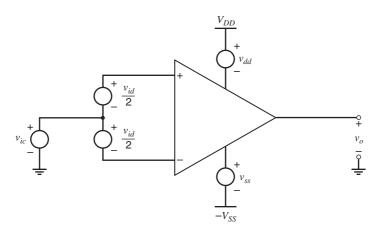

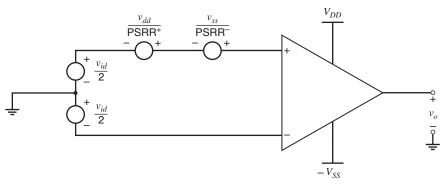

- 6.2.6 Power-Supply Rejection Ratio (PSRR) 418

- 6.2.7 Input Resistance 420

- 6.2.8 Output Resistance 420

- 6.2.9 Frequency Response 420

- 6.2.10 Operational-Amplifier Equivalent Circuit 420

- 6.3 Basic Two-Stage MOS Operational Amplifiers 421

- 6.3.1 Input Resistance, Output Resistance, and Open-Circuit Voltage Gain 422

- 6.3.2 Output Swing 423

- 6.3.3 Input Offset Voltage 424

- 6.3.4 Common-Mode Rejection Ratio 427

- 6.3.5 Common-Mode Input Range 427

- 6.3.6 Power-Supply Rejection Ratio (PSRR) 430

- 6.3.7 Effect of Overdrive Voltages 434

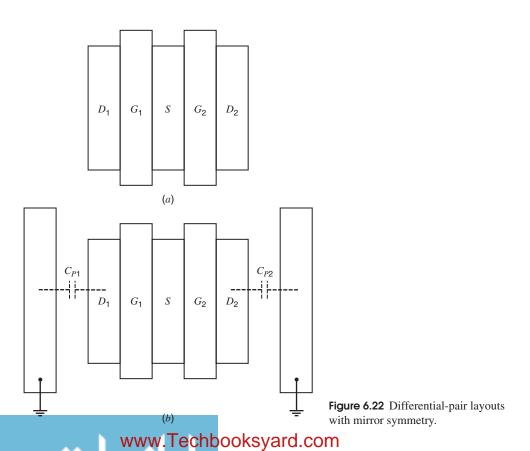

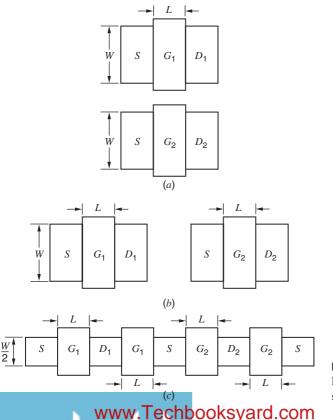

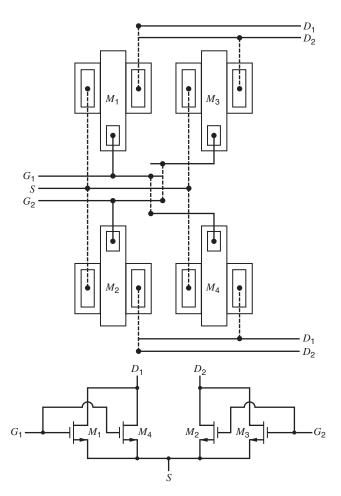

- 6.3.8 Layout Considerations 435

- 6.4 Two-Stage MOS Operational Amplifiers with Cascodes 438

- 6.5 MOS Telescopic-Cascode Operational Amplifiers 439

- 6.6 MOS Folded-Cascode Operational Amplifiers 442

- 6.7 MOS Active-Cascode Operational Amplifiers 446

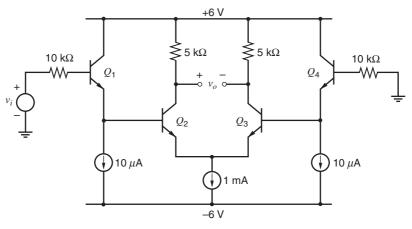

- 6.8 Bipolar Operational Amplifiers 448

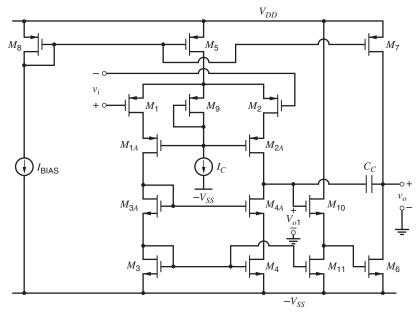

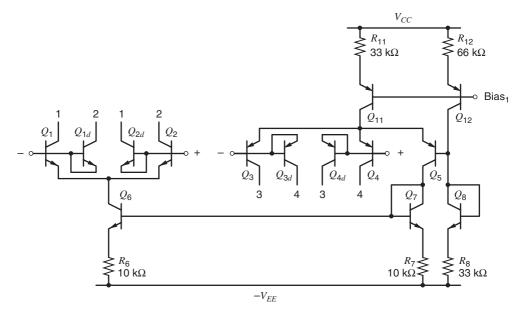

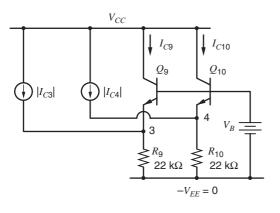

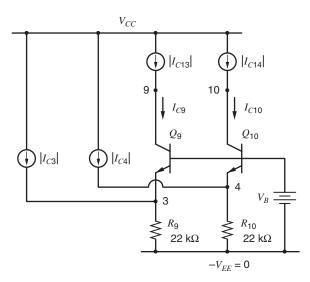

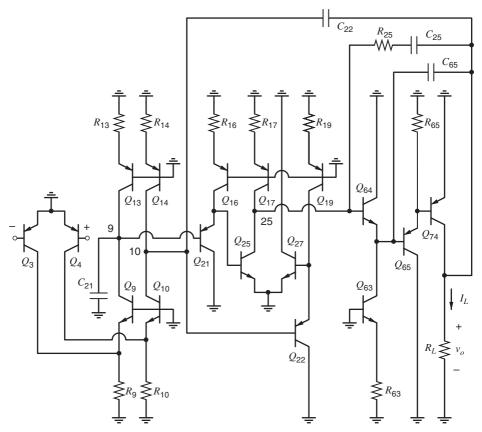

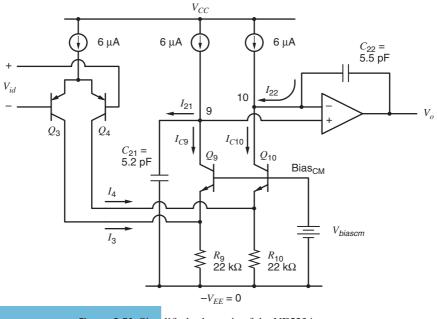

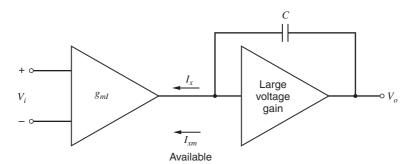

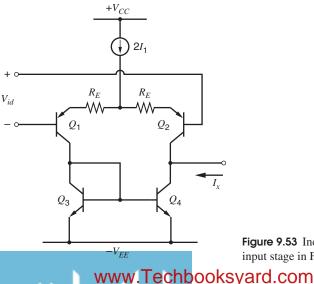

- 6.8.1 The dc Analysis of the NE5234 Operational Amplifier 452

- 6.8.2 Transistors that Are Normally Off 467

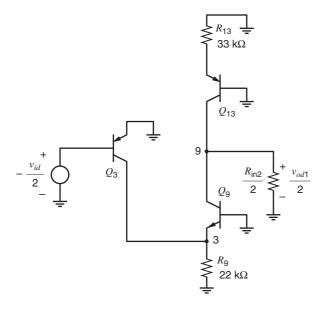

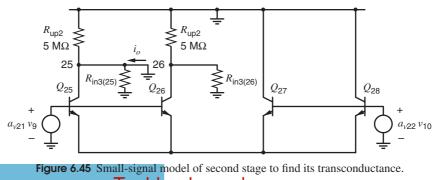

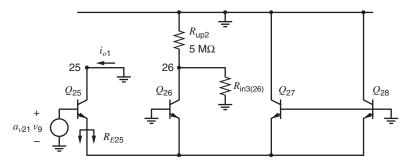

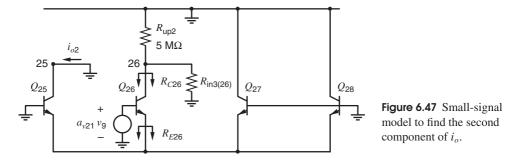

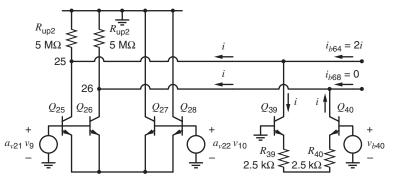

- 6.8.3 Small-Signal Analysis of the NE5234 Operational Amplifier 469

- 6.8.4 Calculation of the Input Offset Voltage and Current of the NE5234 477

### CHAPTER 7 Frequency Response of Integrated Circuits 490

- 7.1 Introduction 490

- 7.2 Single-Stage Amplifiers 490

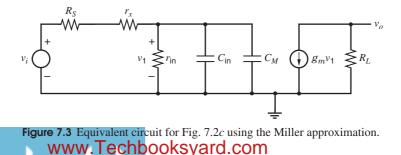

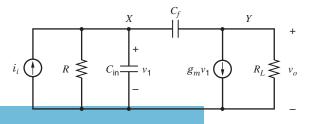

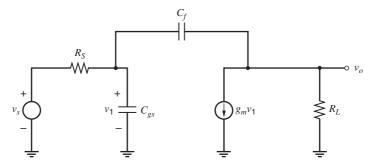

- 7.2.1 Single-Stage Voltage Amplifiers and the Miller Effect 490

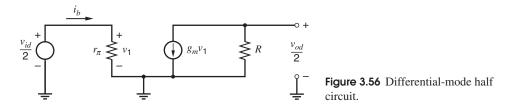

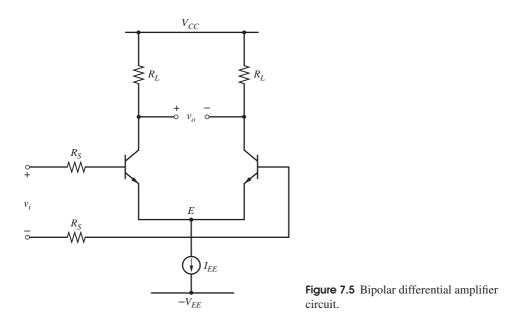

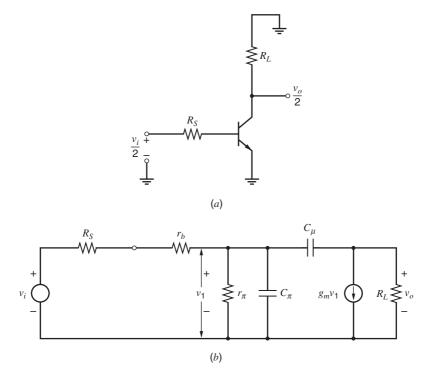

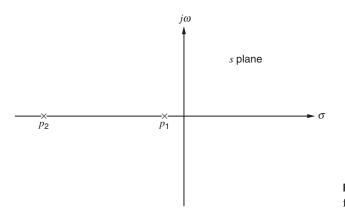

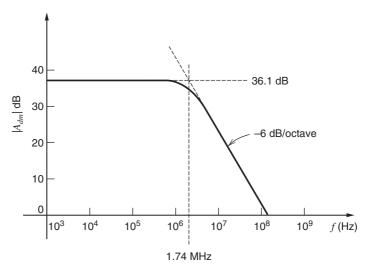

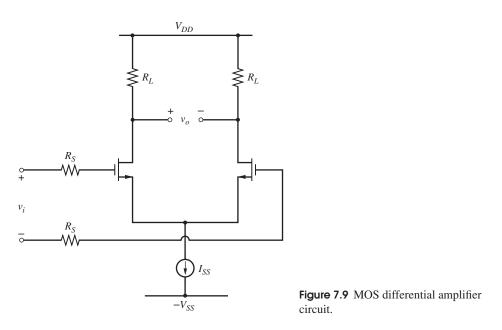

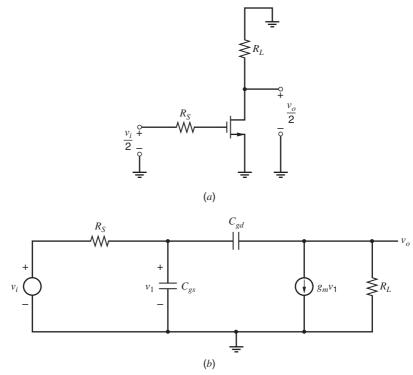

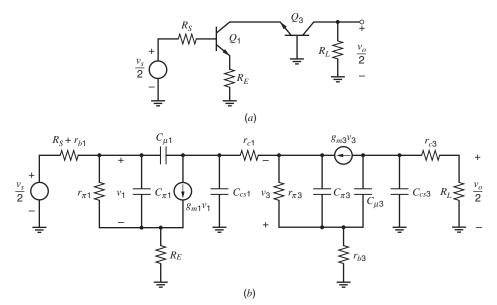

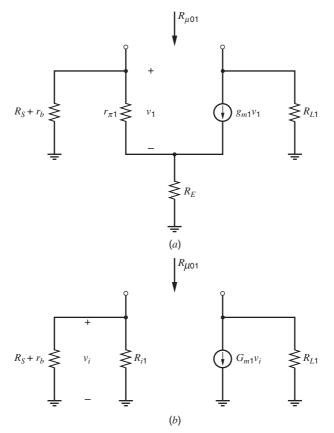

- 7.2.1.1 The Bipolar Differential Amplifier: Differential-Mode Gain 495

- 7.2.1.2 The MOS Differential Amplifier: Differential Mode Gain 499

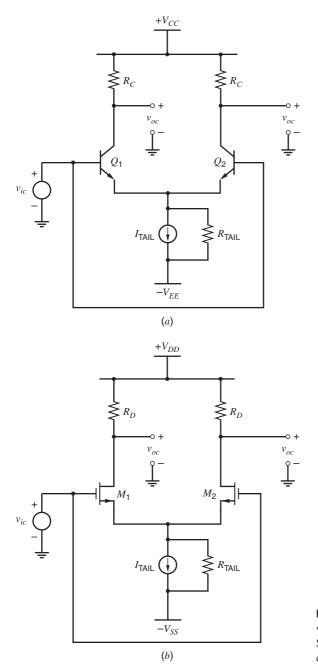

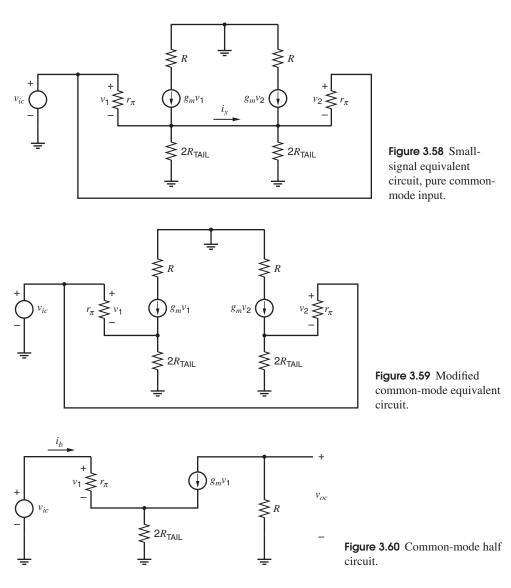

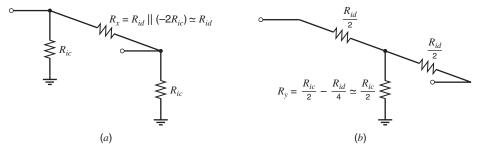

- 7.2.2 Frequency Response of the Common-Mode Gain for a Differential Amplifier 501

- 7.2.3 Frequency Response of Voltage Buffers 503

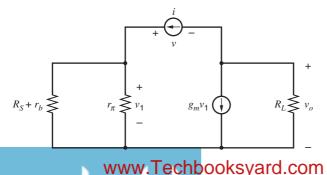

- 7.2.3.1 Frequency Response of the Emitter Follower 505

- 7.2.3.2 Frequency Response of the Source Follower 511

- 7.2.4 Frequency Response of Current Buffers 514

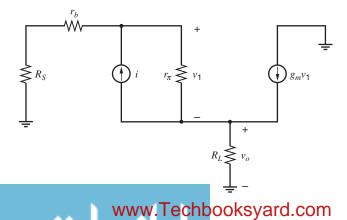

- 7.2.4.1 Common-Base Amplifier Frequency Response 516

- 7.2.4.2 Common-Gate Amplifier

Frequency Response 517

- 7.3 Multistage Amplifier Frequency Response 518

- 7.3.1 Dominant-Pole Approximation 518

- 7.3.2 Zero-Value Time Constant Analysis 519

- 7.3.3 Cascode Voltage-Amplifier Frequency Response 524

- 7.3.4 Cascode Frequency Response 527

- 7.3.5 Frequency Response of a Current Mirror Loading a Differential Pair 534

- 7.3.6 Short-Circuit Time Constants 536

- 7.4 Analysis of the Frequency Response of the NE5234 Op Amp 539

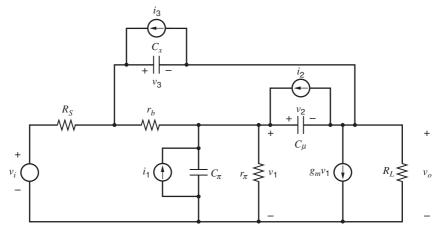

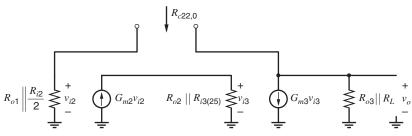

- 7.4.1 High-Frequency Equivalent Circuit of the NE5234 539

- 7.4.2 Calculation of the -3-dB Frequency of the NE5234 540

- 7.4.3 Nondominant Poles of the NE5234 542

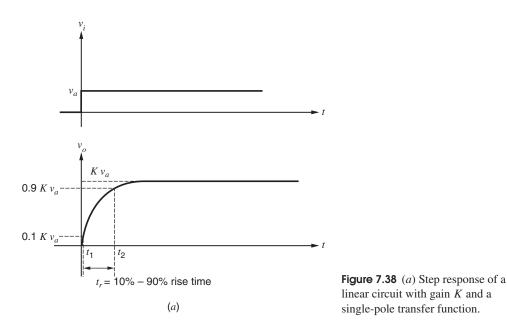

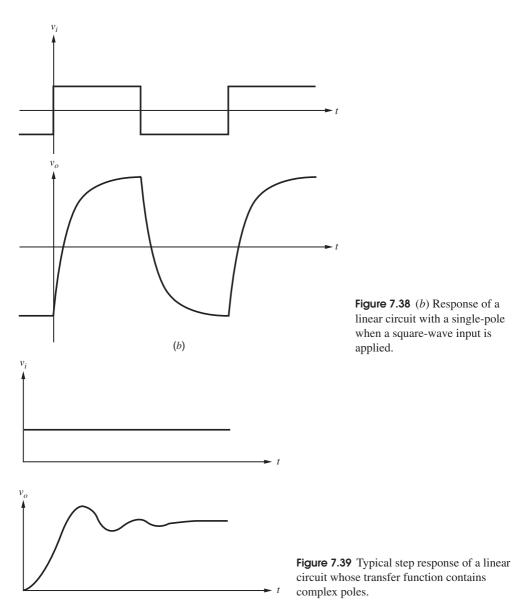

| 7.5 | Relation Between Fre | equency Response |

|-----|----------------------|------------------|

|     | and Time Response    | 542              |

## CHAPTER 8

#### Feedback 553

- 8.1 Ideal Feedback Equation 553

- 8.2 Gain Sensitivity 555

- 8.3 Effect of Negative Feedback on Distortion 555

- 8.4 Feedback Configurations 557

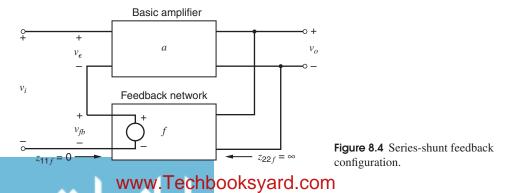

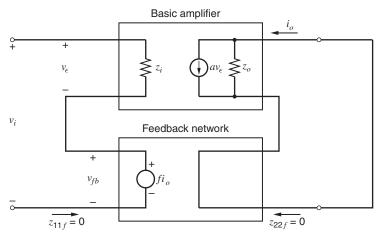

- 8.4.1 Series-Shunt Feedback 557

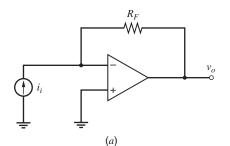

- 8.4.2 Shunt-Shunt Feedback 560

- 8.4.3 Shunt-Series Feedback 561

- 8.4.4 Series-Series Feedback 562

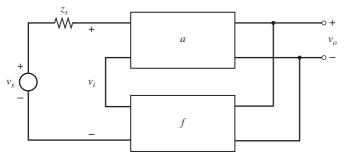

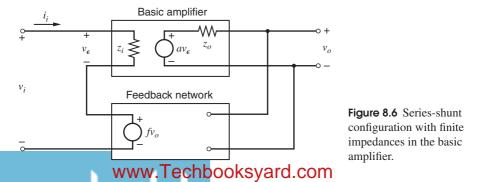

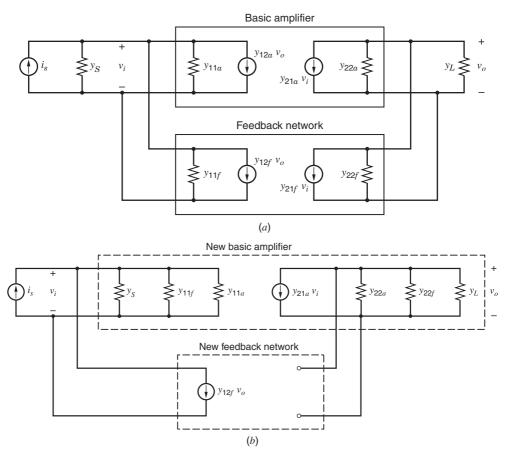

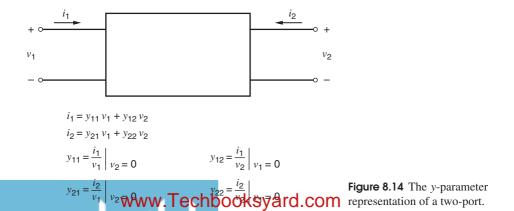

- 8.5 Practical Configurations and the Effect of Loading 563

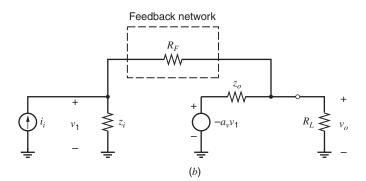

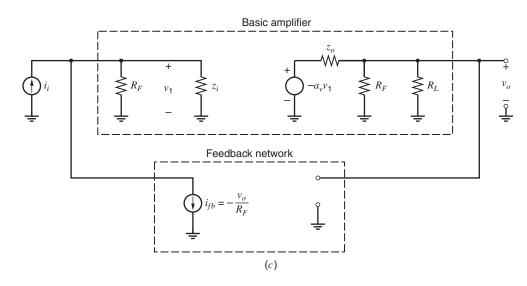

- 8.5.1 Shunt-Shunt Feedback 563

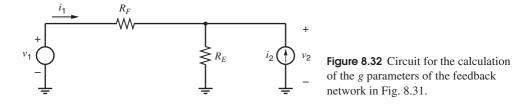

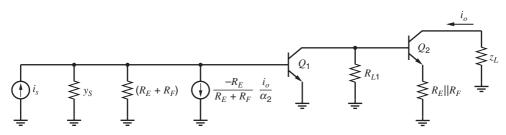

- 8.5.2 Series-Series Feedback 569

- 8.5.3 Series-Shunt Feedback 579

- 8.5.4 Shunt-Series Feedback 583

- 8.5.5 Summary 587

- 8.6 Single-Stage Feedback 587

- 8.6.1 Local Series-Series Feedback 587

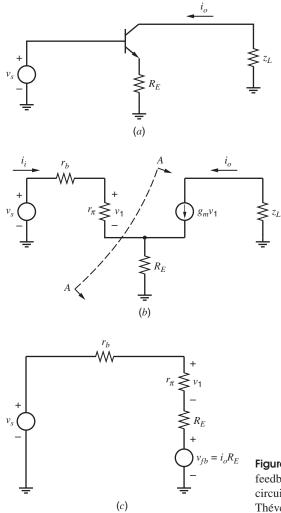

- 8.6.2 Local Series-Shunt Feedback 591

- 8.7 The Voltage Regulator as a Feedback Circuit 593

- 8.8 Feedback Circuit Analysis Using Return Ratio 599

- 8.8.1 Closed-Loop Gain Using Return Ratio 601

- 8.8.2 Closed-Loop Impedance Formula Using Return Ratio 607

- 8.8.3 Summary—Return-Ratio Analysis 612

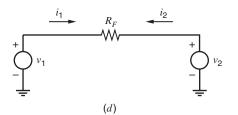

- 8.9 Modeling Input and Output Ports in Feedback Circuits 613

### CHAPTER 9

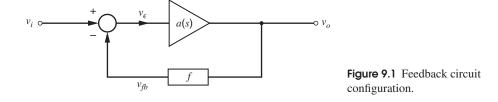

## Frequency Response and Stability of Feedback Amplifiers 624

- 9.1 Introduction 624

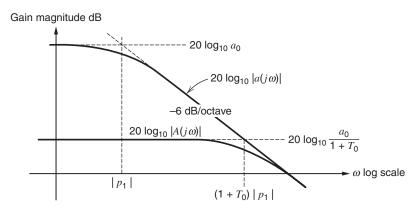

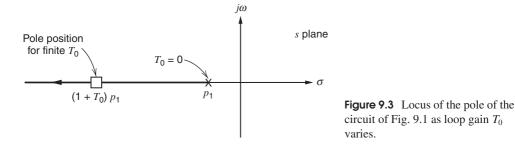

- 9.2 Relation Between Gain and Bandwidth in Feedback Amplifiers 624

- 9.3 Instability and the Nyquist Criterion 626

- 9.4 Compensation 633

- 9.4.1 Theory of Compensation 633

- 9.4.2 Methods of Compensation 637

- 9.4.3 Two-Stage MOS Amplifier Compensation 643

- 9.4.4 Compensation of Single-Stage CMOS Op Amps 650

- 9.4.5 Nested Miller Compensation 654

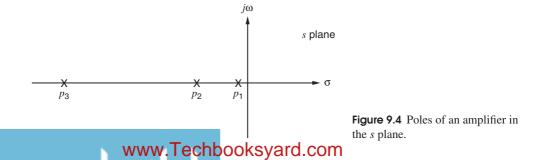

- 9.5 Root-Locus Techniques 664

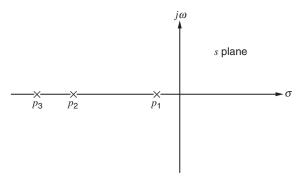

- 9.5.1 Root Locus for a Three-Pole Transfer Function 665

- 9.5.2 Rules for Root-Locus Construction 667

- 9.5.3 Root Locus for Dominant-Pole Compensation 676

- 9.5.4 Root Locus for Feedback-Zero Compensation 677

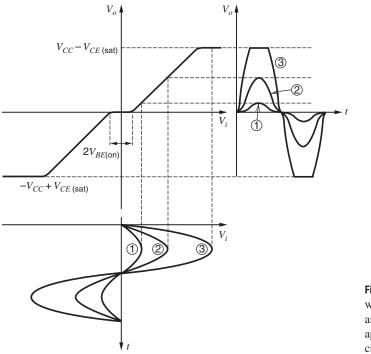

- 9.6 Slew Rate 681

- 9.6.1 Origin of Slew-Rate Limitations 681

- 9.6.2 Methods of Improving Slew-Rate in Two-Stage Op Amps 685

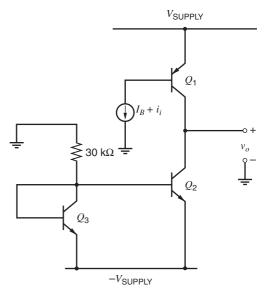

- 9.6.3 Improving Slew-Rate in Bipolar Op Amps 687

- 9.6.4 Improving Slew-Rate in MOS Op Amps 688

- 9.6.5 Effect of Slew-Rate Limitations on Large-Signal Sinusoidal Performance 692

- A.9.1 Analysis in Terms of Return-Ratio Parameters 693

- A.9.2 Roots of a Quadratic Equation 694

#### CHAPTER 10 Nonlinear Analog Circuits 704

- 10.1 Introduction 704

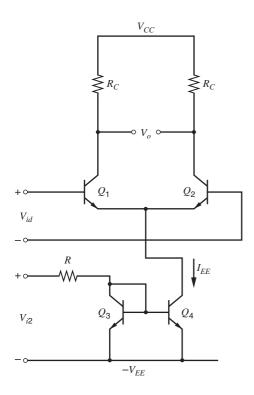

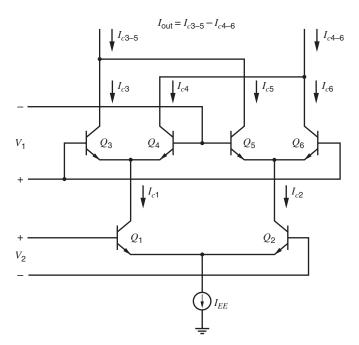

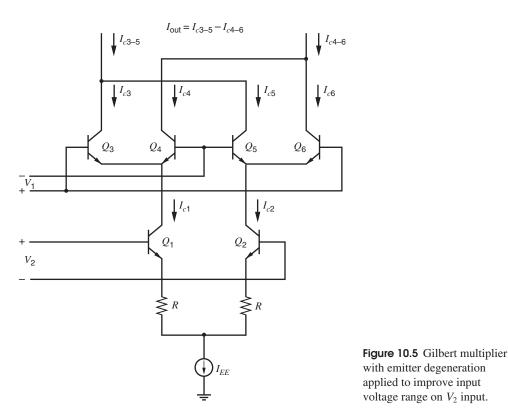

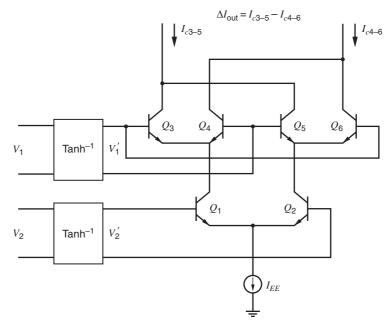

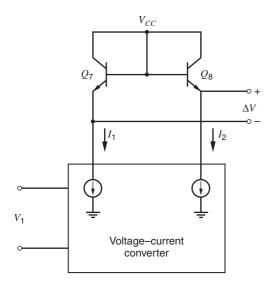

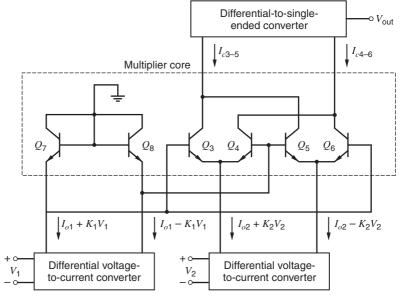

- 10.2 Analog Multipliers Employing the Bipolar Transistor 704

- 10.2.1 The Emitter-Coupled Pair as a Simple Multiplier 704

- 10.2.2 The dc Analysis of the Gilbert Multiplier Cell 706

- 10.2.3 The Gilbert Cell as an Analog Multiplier 708

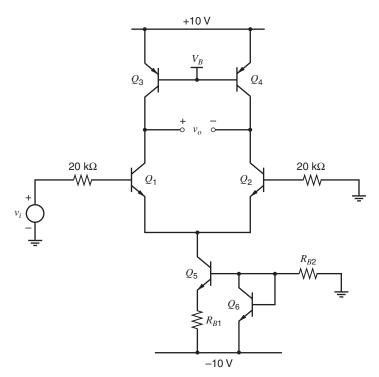

- 10.2.4 A Complete Analog Multiplier 711

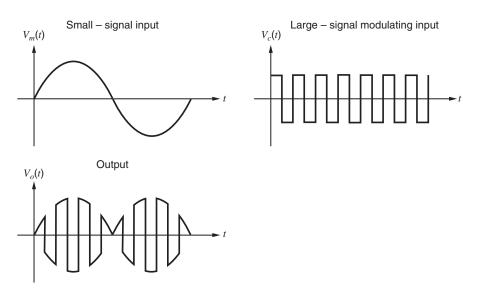

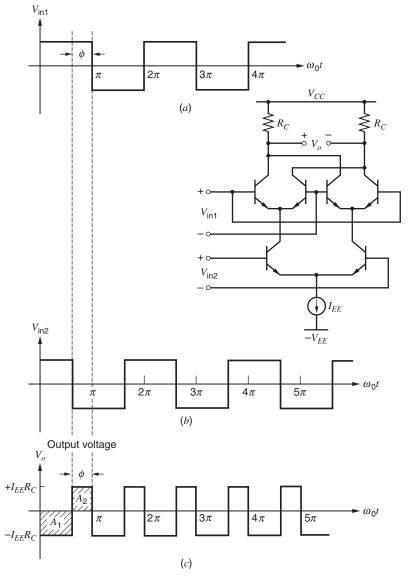

- 10.2.5 The Gilbert Multiplier Cell as a Balanced Modulator and Phase Detector 712

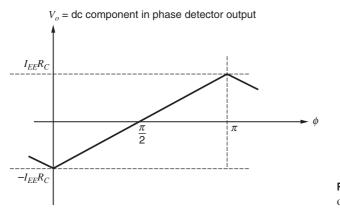

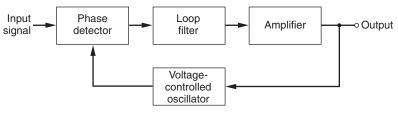

- 10.3 Phase-Locked Loops (PLL) 716

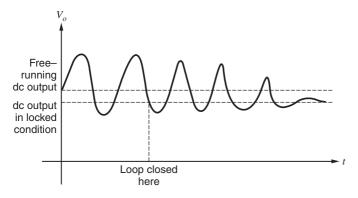

- 10.3.1 Phase-Locked Loop Concepts 716

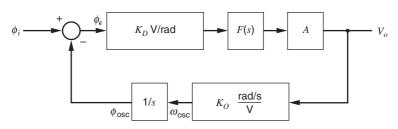

- 10.3.2 The Phase-Locked Loop in the Locked Condition 718

- 10.3.3 Integrated-Circuit Phase-Locked Loops 727

- 10.4 Nonlinear Function Synthesis 731

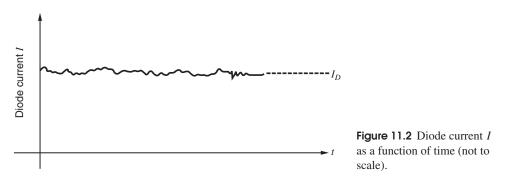

## CHAPTER 11 Noise in Integrated Circuits 736

- 11.1 Introduction 736

- 11.2 Sources of Noise 736

- 11.2.1 Shot Noise 736

- 11.2.2 Thermal Noise 740

- 11.2.3 Flicker Noise (1/f Noise) 741

- 11.2.4 Burst Noise (Popcorn Noise) 742

- 11.2.5 Avalanche Noise 743

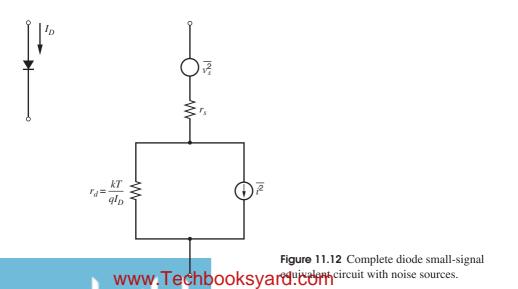

- 11.3 Noise Models of Integrated-Circuit Components 744

- 11.3.1 Junction Diode 744

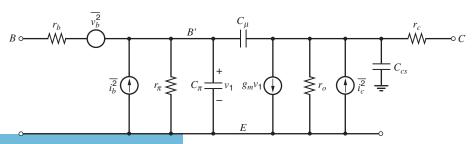

- 11.3.2 Bipolar Transistor 745

- 11.3.3 MOS Transistor 746

- 11.3.4 Resistors 747

- 11.3.5 Capacitors and Inductors 747

### 11.4 Circuit Noise Calculations 748

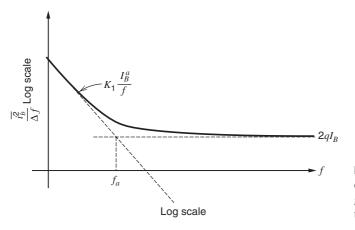

- 11.4.1 Bipolar Transistor Noise Performance 750

- 11.4.2 Equivalent Input Noise and the Minimum Detectable Signal 754

- 11.5 Equivalent Input Noise Generators 756

- 11.5.1 Bipolar Transistor Noise Generators 757

- 11.5.2 MOS Transistor Noise Generators 762

- 11.6 Effect of Feedback on Noise Performance 764

- 11.6.1 Effect of Ideal Feedback on Noise Performance 764

- 11.6.2 Effect of Practical Feedback on Noise Performance 765

- 11.7 Noise Performance of Other Transistor Configurations 771

- 11.7.1 Common-Base Stage Noise Performance 771

- 11.7.2 Emitter-Follower Noise Performance 773

- 11.7.3 Differential-Pair Noise Performance 773

- 11.8 Noise in Operational Amplifiers 776

- 11.9 Noise Bandwidth 782

- 11.10 Noise Figure and Noise Temperature 786

- 11.10.1 Noise Figure 786

- 11.10.2 Noise Temperature 790

#### CHAPTER 12

## Fully Differential Operational Amplifiers 796

- 12.1 Introduction 796

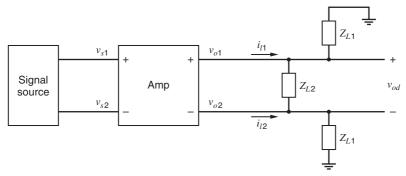

- 12.2 Properties of Fully Differential Amplifiers 796

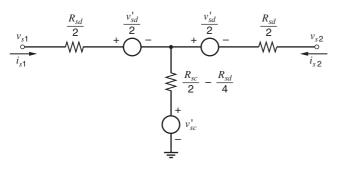

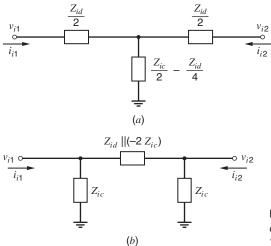

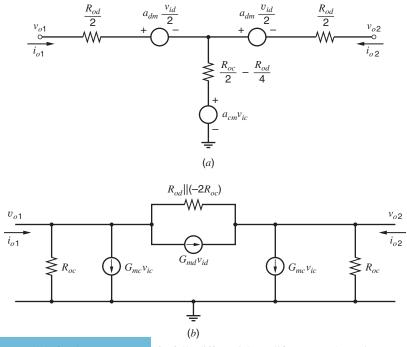

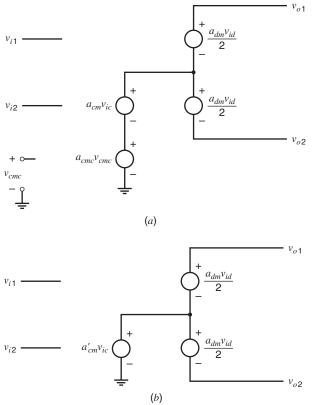

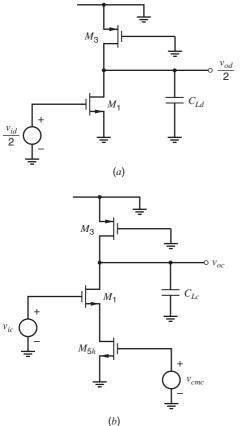

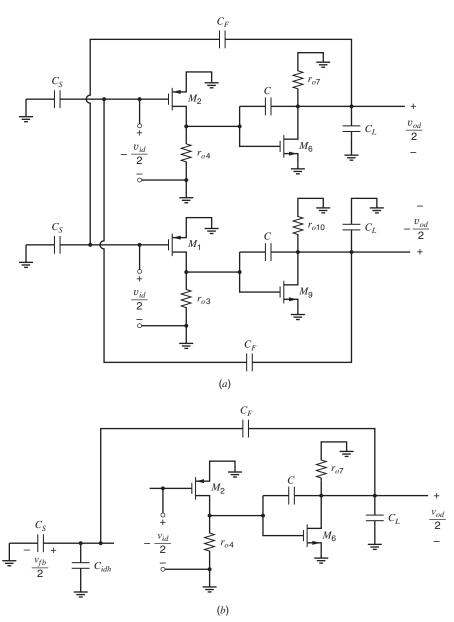

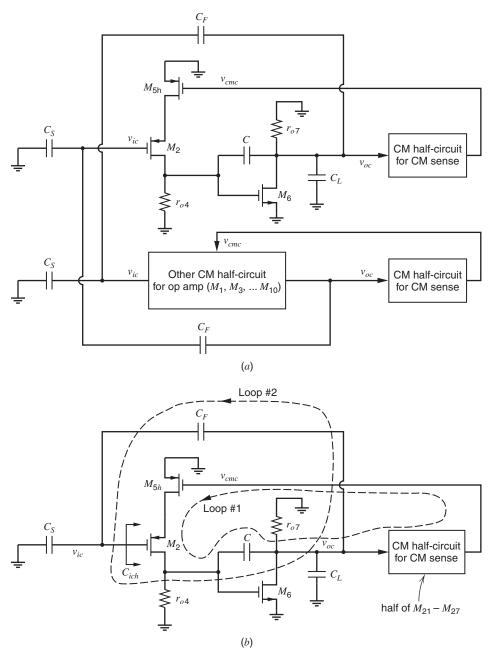

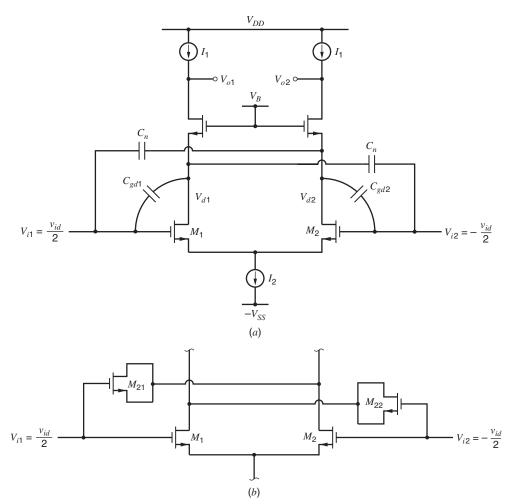

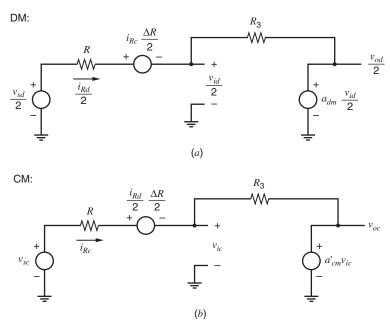

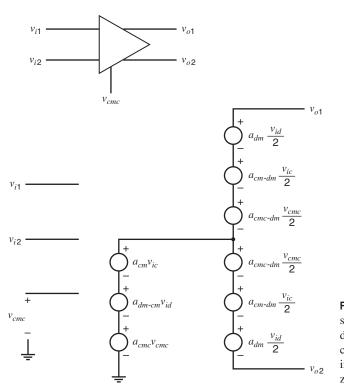

- 12.3 Small-Signal Models for Balanced Differential Amplifiers 799

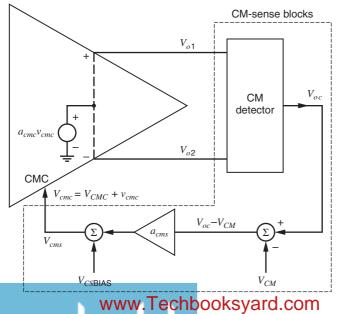

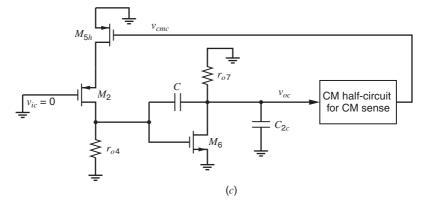

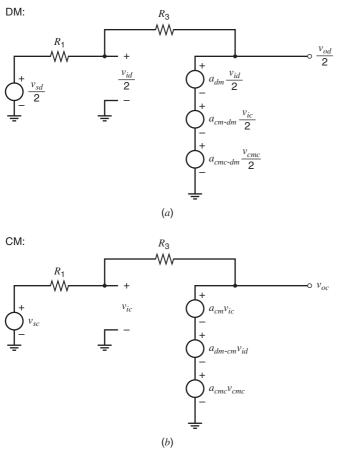

- 12.4 Common-Mode Feedback 804

- 12.4.1 Common-Mode Feedback at Low Frequencies 805

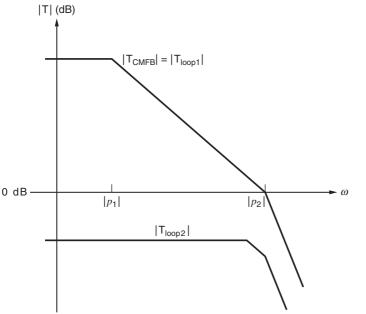

- 12.4.2 Stability and Compensation Considerations in a CMFB Loop 810

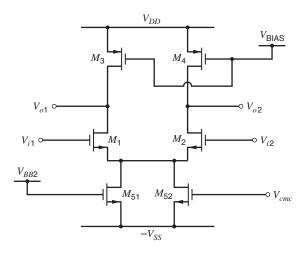

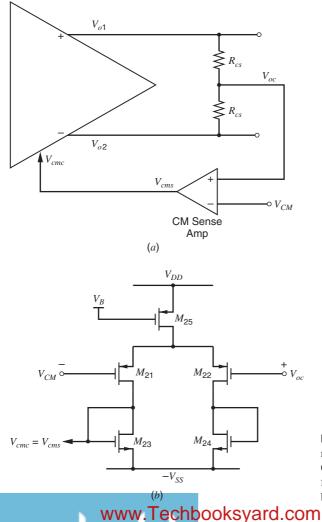

- 12.5 CMFB Circuits 811

- 12.5.1 CMFB Using Resistive Divider and Amplifier 812

- 12.5.2 CMFB Using Two Differential Pairs 816

- 12.5.3 CMFB Using Transistors in the Triode Region 819

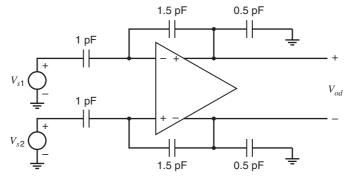

- 12.5.4 Switched-Capacitor CMFB 821

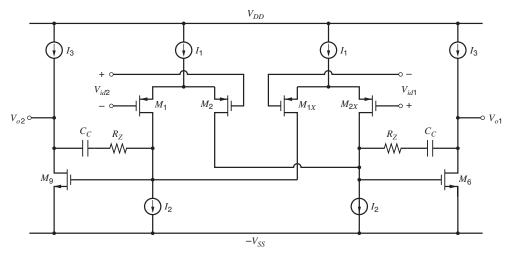

- 12.6 Fully Differential Op Amps 823

- 12.6.1 A Fully Differential Two-Stage Op Amp 823

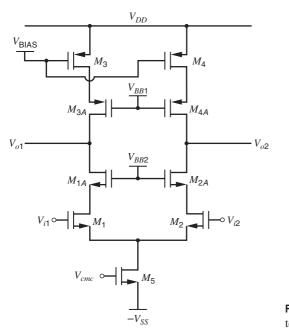

- 12.6.2 Fully Differential Telescopic Cascode Op Amp 833

#### xiv Symbol Convention

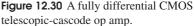

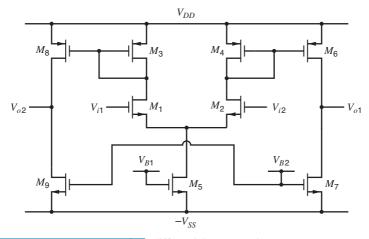

- 12.6.3 Fully Differential Folded-Cascode Op Amp 834

- 12.6.4 A Differential Op Amp with Two Differential Input Stages 835

- 12.6.5 Neutralization 835

- 12.7 Unbalanced Fully Differential Circuits 838

- 12.8 Bandwidth of the CMFB Loop 844

- 12.9 Analysis of a CMOS Fully Differential Folded-Cascode Op Amp 845

- 12.9.1 DC Biasing 848

- 12.9.2 Low-Frequency Analysis 850

- 12.9.3 Frequency and Time Responses in a Feedback Application 856

**Index** 871

## **Symbol Convention**

Unless otherwise stated, the following symbol convention is used in this book. *Bias* or *dc* quantities, such as transistor collector current  $I_C$  and collector-emitter voltage  $V_{CE}$ , are represented by uppercase symbols with uppercase subscripts. Small-signal quantities, such as the incremental change in transistor collector current  $i_c$ , are represented by lowercase symbols with lowercase subscripts. Elements such as transconductance  $g_m$  in small-signal equivalent circuits are represented in the same way. Finally, quantities such as *total* collector current  $I_c$ , which represent the sum of the bias quantity *and* the signal quantity, are represented by an uppercase symbol with a lowercase subscript.

# Models for Integrated-Circuit **Active Devices**

## 1.1 Introduction

The analysis and design of integrated circuits depend heavily on the utilization of suitable models for integrated-circuit components. This is true in hand analysis, where fairly simple models are generally used, and in computer analysis, where more complex models are encountered. Since any analysis is only as accurate as the model used, it is essential that the circuit designer have a thorough understanding of the origin of the models commonly utilized and the degree of approximation involved in each.

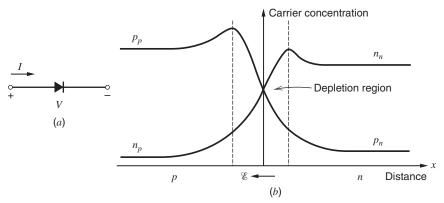

This chapter deals with the derivation of large-signal and small-signal models for integrated-circuit devices. The treatment begins with a consideration of the properties of pn junctions, which are basic parts of most integrated-circuit elements. Since this book is primarily concerned with circuit analysis and design, no attempt has been made to produce a comprehensive treatment of semiconductor physics. The emphasis is on summarizing the basic aspects of semiconductor-device behavior and indicating how these can be modeled by equivalent circuits.

## 1.2 Depletion Region of a pn Junction

The properties of reverse-biased *pn* junctions have an important influence on the characteristics of many integrated-circuit components. For example, reverse-biased pn junctions exist between many integrated-circuit elements and the underlying substrate, and these junctions all contribute voltage-dependent parasitic capacitances. In addition, a number of important characteristics of active devices, such as breakdown voltage and output resistance, depend directly on the properties of the depletion region of a reverse-biased *pn* junction. Finally, the basic operation of the junction field-effect transistor is controlled by the width of the depletion region of a *pn* junction. Because of its importance and application to many different problems, an analysis of the depletion region of a reverse-biased *pn* junction is considered below. The properties of forward-biased pn junctions are treated in Section 1.3 when bipolar-transistor operation is described.

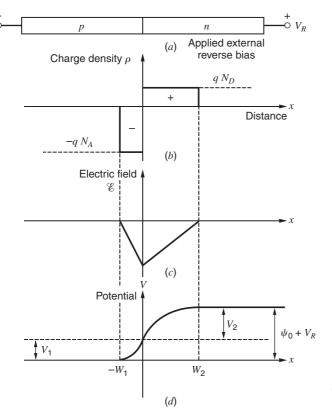

Consider a *pn* junction under reverse bias as shown in Fig. 1.1. Assume *constant doping* densities of  $N_D$  atoms/cm<sup>3</sup> in the *n*-type material and  $N_A$  atoms/cm<sup>3</sup> in the *p*-type material. (The characteristics of junctions with nonconstant doping densities will be described later.) Due to the difference in carrier concentrations in the *p*-type and *n*-type regions, there exists a region at the junction where the mobile holes and electrons have been removed, leaving the fixed acceptor and donor ions. Each acceptor atom carries a negative charge and each donor atom carries a positive charge, so that the region near the junction is one of significant space charge and resulting high electric field. This is called the *depletion* region or *space-charge*

Figure 1.1 The abrupt junction under reverse bias  $V_R$ . (*a*) Schematic. (*b*) Charge density. (*c*) Electric field. (*d*) Electrostatic potential.

region. It is assumed that the edges of the depletion region are sharply defined as shown in Fig. 1.1, and this is a good approximation in most cases.

For zero applied bias, there exists a voltage  $\psi_0$  across the junction called the *built-in* potential. This potential opposes the diffusion of mobile holes and electrons across the junction in equilibrium and has a value<sup>1</sup>

$$\psi_0 = V_T \ln \frac{N_A N_D}{n_i^2} \tag{1.1}$$

where

$$V_T = \frac{kT}{q} \simeq 26 \text{ mV} \text{ at } 300^\circ \text{K}$$

the quantity  $n_i$  is the intrinsic carrier concentration in a pure sample of the semiconductor and  $n_i \simeq 1.5 \times 10^{10} \text{cm}^{-3}$  at 300°K for silicon.

In Fig. 1.1 the built-in potential is augmented by the applied reverse bias,  $V_R$ , and the total voltage across the junction is  $(\psi_0 + V_R)$ . If the depletion region penetrates a distance  $W_1$  into the *p*-type region and  $W_2$  into the *n*-type region, then we require

$$W_1 N_A = W_2 N_D \tag{1.2}$$

because the total charge per unit area on either side of the junction must be equal in magnitude but opposite in sign.

Poisson's equation in one dimension requires that

$$\frac{d^2 V}{dx^2} = -\frac{\rho}{\epsilon} = \frac{qN_A}{\epsilon} \quad \text{for} \quad -W_1 < x < 0 \tag{1.3}$$

where  $\rho$  is the charge density, q is the electron charge (1.6 × 10<sup>-19</sup> coulomb), and  $\epsilon$  is the permittivity of the silicon (1.04 × 10<sup>-12</sup> farad/cm). The permittivity is often expressed as

$$\epsilon = K_S \epsilon_0 \tag{1.4}$$

where  $K_S$  is the dielectric constant of silicon and  $\epsilon_0$  is the permittivity of free space (8.86 × 10<sup>-14</sup> F/cm). Integration of (1.3) gives

$$\frac{dV}{dx} = \frac{qN_A}{\epsilon}x + C_1 \tag{1.5}$$

where  $C_1$  is a constant. However, the electric field  $\mathscr{E}$  is given by

$$\mathscr{E} = -\frac{dV}{dx} = -\left(\frac{qN_A}{\epsilon}x + C_1\right) \tag{1.6}$$

Since there is zero electric field outside the depletion region, a boundary condition is

$\mathscr{E} = 0$  for  $x = -W_1$

and use of this condition in (1.6) gives

$$\mathscr{E} = -\frac{qN_A}{\epsilon}(x+W_1) = -\frac{dV}{dx} \quad \text{for} \quad -W_1 < x < 0 \tag{1.7}$$

Thus the dipole of charge existing at the junction gives rise to an electric field that varies linearly with distance.

Integration of (1.7) gives

$$V = \frac{qN_A}{\epsilon} \left(\frac{x^2}{2} + W_1 x\right) + C_2 \tag{1.8}$$

If the zero for potential is arbitrarily taken to be the potential of the neutral *p*-type region, then a second boundary condition is

$$V = 0$$

for  $x = -W_1$

and use of this in (1.8) gives

$$V = \frac{qN_A}{\epsilon} \left( \frac{x^2}{2} + W_1 x + \frac{W_1^2}{2} \right) \quad \text{for} \quad -W_1 < x < 0 \tag{1.9}$$

At x = 0, we define  $V = V_1$ , and then (1.9) gives

$$V_1 = \frac{qN_A}{\epsilon} \frac{W_1^2}{2} \tag{1.10}$$

If the potential difference from x = 0 to  $x = W_2$  is  $V_2$ , then it follows that

$$V_2 = \frac{qN_D}{\epsilon} \frac{W_2^2}{2} \tag{1.11}$$

and thus the total voltage across the junction is

$$\psi_0 + V_R = V_1 + V_2 = \frac{q}{2\epsilon} (N_A W_1^2 + N_D W_2^2)$$

(1.12)

#### 4 Chapter 1 Models for Integrated-Circuit Active Devices

Substitution of (1.2) in (1.12) gives

$$\psi_0 + V_R = \frac{q W_1^2 N_A}{2\epsilon} \left( 1 + \frac{N_A}{N_D} \right) \tag{1.13}$$

From (1.13), the penetration of the depletion layer into the *p*-type region is

$$W_1 = \left[\frac{2\epsilon(\psi_0 + V_R)}{qN_A\left(1 + \frac{N_A}{N_D}\right)}\right]^{1/2}$$

(1.14)

Similarly,

$$W_2 = \left[\frac{2\epsilon(\psi_0 + V_R)}{qN_D\left(1 + \frac{N_D}{N_A}\right)}\right]^{1/2}$$

(1.15)

Equations 1.14 and 1.15 show that the depletion regions extend into the *p*-type and *n*-type regions in *inverse* relation to the impurity concentrations and in proportion to  $\sqrt{\psi_0 + V_R}$ . If either  $N_D$  or  $N_A$  is much larger than the other, the depletion region exists almost entirely in the *lightly doped* region.

#### EXAMPLE

An abrupt *pn* junction in silicon has doping densities  $N_A = 10^{15}$  atoms/cm<sup>3</sup> and  $N_D = 10^{16}$  atoms/cm<sup>3</sup>. Calculate the junction built-in potential, the depletion-layer depths, and the maximum field with 10 V reverse bias.

From (1.1)

$$\psi_0 = 26 \ln \frac{10^{15} \times 10^{16}}{2.25 \times 10^{20}} \text{ mV} = 638 \text{ mV} \text{ at } 300^{\circ} \text{K}$$

From (1.14) the depletion-layer depth in the *p*-type region is

$$W_1 = \left(\frac{2 \times 1.04 \times 10^{-12} \times 10.64}{1.6 \times 10^{-19} \times 10^{15} \times 1.1}\right)^{1/2} = 3.5 \times 10^{-4} \text{cm}$$

= 3.5 \mum (where 1 \mum = 1 micrometer = 10^{-6} m)

The depletion-layer depth in the more heavily doped *n*-type region is

$$W_2 = \left(\frac{2 \times 1.04 \times 10^{-12} \times 10.64}{1.6 \times 10^{-19} \times 10^{16} \times 11}\right)^{1/2} = 0.35 \times 10^{-4} \text{ cm} = 0.35 \text{ }\mu\text{m}$$

Finally, from (1.7) the maximum field that occurs for x = 0 is

$$\mathscr{C}_{\max} = -\frac{qN_A}{\epsilon} W_1 = -1.6 \times 10^{-19} \times \frac{10^{15} \times 3.5 \times 10^{-4}}{1.04 \times 10^{-12}}$$

= -5.4 × 10<sup>4</sup> V/cm

Note the large magnitude of this electric field.

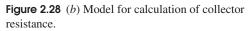

### 1.2.1 Depletion-Region Capacitance

Since there is a *voltage-dependent charge* Q associated with the depletion region, we can calculate a small-signal capacitance  $C_j$  as follows:

$$C_j = \frac{dQ}{dV_R} = \frac{dQ}{dW_1} \frac{dW_1}{dV_R}$$

(1.16)

Now

$$dQ = AqN_A dW_1 \tag{1.17}$$

where A is the cross-sectional area of the junction. Differentiation of (1.14) gives

$$\frac{dW_1}{dV_R} = \left[\frac{\epsilon}{2qN_A\left(1 + \frac{N_A}{N_D}\right)(\psi_0 + V_R)}\right]^{1/2}$$

(1.18)

Use of (1.17) and (1.18) in (1.16) gives

$$C_j = A \left[ \frac{q \epsilon N_A N_D}{2(N_A + N_D)} \right]^{1/2} \frac{1}{\sqrt{\psi_0 + V_R}}$$

(1.19)

The above equation was derived for the case of reverse bias  $V_R$  applied to the diode. However, it is valid for positive bias voltages as long as the forward current flow is small. Thus, if  $V_D$  represents the bias on the junction (positive for forward bias, negative for reverse bias), then (1.19) can be written as

$$C_{j} = A \left[ \frac{q \epsilon N_{A} N_{D}}{2(N_{A} + N_{D})} \right]^{1/2} \frac{1}{\sqrt{\psi_{0} - V_{D}}}$$

(1.20)

$$=\frac{C_{j0}}{\sqrt{1-\frac{V_D}{\psi_0}}}$$

(1.21)

where  $C_{i0}$  is the value of  $C_i$  for  $V_D = 0$ .

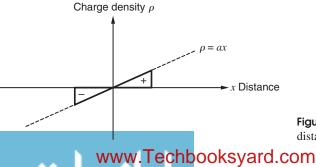

Equations 1.20 and 1.21 were derived using the assumption of constant doping in the *p*-type and *n*-type regions. However, many practical diffused junctions more closely approach a *graded* doping profile as shown in Fig. 1.2. In this case, a similar calculation yields

$$C_{j} = \frac{C_{j0}}{\sqrt[3]{1 - \frac{V_{D}}{\psi_{0}}}}$$

(1.22)

**Figure 1.2** Charge density versus distance in a graded junction.

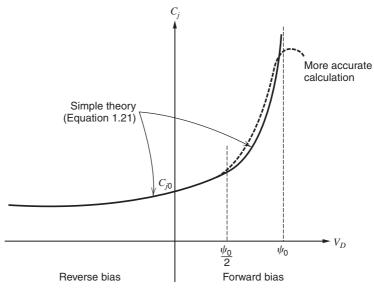

**Figure 1.3** Behavior of *pn* junction depletion-layer capacitance  $C_j$  as a function of bias voltage  $V_D$ .

Note that both (1.21) and (1.22) predict values of  $C_j$  approaching infinity as  $V_D$  approaches  $\psi_0$ . However, the current flow in the diode is then appreciable and the equations are no longer valid. A more exact analysis<sup>2,3</sup> of the behavior of  $C_j$  as a function of  $V_D$  gives the result shown in Fig. 1.3. For forward bias voltages up to about  $\psi_0/2$ , the values of  $C_j$  predicted by (1.21) are very close to the more accurate value. As an approximation, some computer programs approximate  $C_j$  for  $V_D > \psi_0/2$  by a linear extrapolation of (1.21) or (1.22).

### EXAMPLE

If the zero-bias capacitance of a diffused junction is 3 pF and  $\psi_0 = 0.5$  V, calculate the capacitance with 10 V reverse bias. Assume the doping profile can be approximated by an abrupt junction.

From (1.21)

$$C_j = \frac{3}{\sqrt{1 + \frac{10}{0.5}}}$$

pF = 0.65 pF

### 1.2.2 Junction Breakdown

From Fig. 1.1c it can be seen that the maximum electric field in the depletion region occurs at the junction, and for an abrupt junction (1.7) yields a value

$$\mathscr{C}_{\max} = -\frac{qN_A}{\epsilon}W_1 \tag{1.23}$$

Substitution of (1.14) in (1.23) gives

$$|\mathscr{E}_{\max}| = \left[\frac{2qN_AN_DV_R}{\epsilon (N_A + N_D)}\right]^{1/2}$$

(1.24)

where  $\psi_0$  has been neglected. Equation 1.24 shows that the maximum field increases as the doping density increases and the reverse bias increases. Although useful for indicating the www.Techbooksyard.com

functional dependence of  $\mathscr{C}_{max}$  on other variables, this equation is strictly valid for an ideal plane junction only. Practical junctions tend to have edge effects that cause somewhat higher values of  $\mathscr{C}_{max}$  due to a concentration of the field at the curved edges of the junction.

Any reverse-biased *pn* junction has a small reverse current flow due to the presence of minority-carrier holes and electrons in the vicinity of the depletion region. These are swept across the depletion region by the field and contribute to the leakage current of the junction. As the reverse bias on the junction is increased, the maximum field increases and the carriers acquire increasing amounts of energy between lattice collisions in the depletion region. At a critical field  $\mathscr{C}_{crit}$  the carriers traversing the depletion region acquire sufficient energy to create new hole-electron pairs in collisions with silicon atoms. This is called the *avalanche process* and leads to a sudden increase in the reverse-bias leakage current since the newly created carriers are also capable of producing avalanche. The value of  $\mathscr{C}_{crit}$  is about  $3 \times 10^5$  V/cm for junction doping densities in the range of  $10^{15}$  to  $10^{16}$  atoms/cm<sup>3</sup>, but it increases slowly as the doping density increases and reaches about  $10^6$  V/cm for doping densities of  $10^{18}$  atoms/cm<sup>3</sup>.

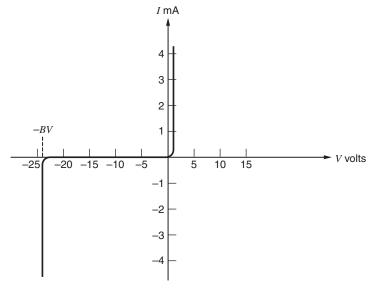

A typical *I-V* characteristic for a junction diode is shown in Fig. 1.4, and the effect of avalanche breakdown is seen by the large increase in reverse current, which occurs as the reverse bias approaches the breakdown voltage *BV*. This corresponds to the maximum field  $\mathscr{C}_{max}$  approaching  $\mathscr{C}_{crit}$ . It has been found empirically<sup>4</sup> that if the normal reverse bias current of the diode is  $I_R$  with no avalanche effect, then the actual reverse current near the breakdown voltage is

$$I_{RA} = MI_R \tag{1.25}$$

where *M* is the *multiplication factor* defined by

$$M = \frac{1}{1 - \left(\frac{V_R}{BV}\right)^n} \tag{1.26}$$

In this equation,  $V_R$  is the reverse bias on the diode and *n* has a value between 3 and 6.

#### 8 Chapter 1 Models for Integrated-Circuit Active Devices

The operation of a *pn* junction in the breakdown region is not inherently destructive. However, the avalanche current flow must be limited by external resistors in order to prevent excessive power dissipation from occurring at the junction and causing damage to the device. Diodes operated in the avalanche region are widely used as voltage references and are called *Zener diodes*. There is another, related process called *Zener breakdown*,<sup>5</sup> which is different from the avalanche breakdown described above. Zener breakdown occurs only in very heavily doped junctions where the electric field becomes large enough (even with small reverse-bias voltages) to strip electrons away from the valence bonds. This process is called *tunneling*, and there is no multiplication effect as in avalanche breakdown. Although the Zener breakdown diodes are commonly referred to as Zener diodes.

The calculations so far have been concerned with the breakdown characteristic of plane abrupt junctions. Practical diffused junctions differ in some respects from these results and the characteristics of these junctions have been calculated and tabulated for use by designers.<sup>5</sup> In particular, edge effects in practical diffused junctions can result in breakdown voltages as much as 50 percent below the value calculated for a plane junction.

#### EXAMPLE

An abrupt plane *pn* junction has doping densities  $N_A = 5 \times 10^{15}$  atoms/cm<sup>3</sup> and  $N_D = 10^{16}$  atoms/cm<sup>3</sup>. Calculate the breakdown voltage if  $\mathscr{C}_{crit} = 3 \times 10^5$  V/cm.

The breakdown voltage is calculated using  $\mathscr{C}_{max} = \mathscr{C}_{crit}$  in (1.24) to give

$$BV = \frac{\epsilon (N_A + N_D)}{2qN_A N_D} \mathcal{E}_{\text{crit}}^2$$

$$= \frac{1.04 \times 10^{-12} \times 15 \times 10^{15}}{2 \times 1.6 \times 10^{-19} \times 5 \times 10^{15} \times 10^{16}} \times 9 \times 10^{10} \text{ V}$$

$$= 88 \text{ V}$$

## 1.3 Large-Signal Behavior of Bipolar Transistors

In this section, the large-signal or dc behavior of bipolar transistors is considered. Large-signal models are developed for the calculation of total currents and voltages in transistor circuits, and such effects as breakdown voltage limitations, which are usually not included in models, are also considered. Second-order effects, such as current-gain variation with collector current and Early voltage, can be important in many circuits and are treated in detail.

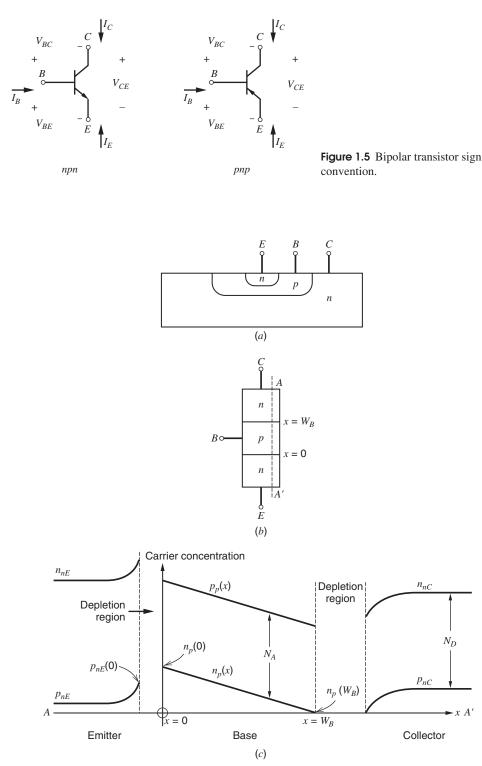

The sign conventions used for bipolar transistor currents and voltages are shown in Fig. 1.5. All bias currents for both *npn* and *pnp* transistors are assumed positive going into the device.

## 1.3.1 Large-Signal Models in the Forward-Active Region

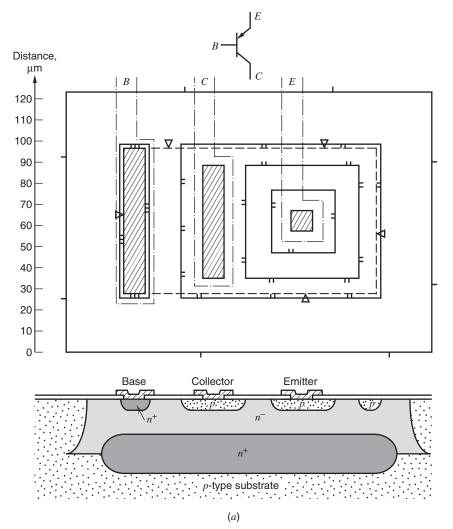

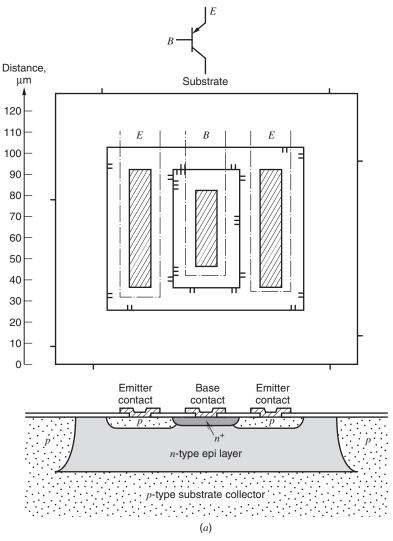

A typical npn planar bipolar transistor structure is shown in Fig. 1.6*a*, where collector, base, and emitter are labeled *C*, *B*, and *E*, respectively. The method of fabricating such transistor structures is described in Chapter 2. It is shown there that the impurity doping density in the base and the emitter of such a transistor is not constant but varies with distance from the top surface. However, many of the characteristics of such a device can be predicted by analyzing the idealized transistor structure shown in Fig. 1.6*b*. In this structure, the base and emitter

**Figure 1.6** (*a*) Cross section of a typical *npn* planar bipolar transistor structure. (*b*) Idealized transistor structure. (*c*) Carrier concentrations along the cross section AA' of the transistor in (*b*). Uniform doping densities are assumed. (Not to scale.)

#### 10 Chapter 1 Models for Integrated-Circuit Active Devices

doping densities are assumed constant, and this is sometimes called a *uniform-base* transistor. Where possible in the following analyses, the equations for the uniform-base analysis are expressed in a form that applies also to nonuniform-base transistors.

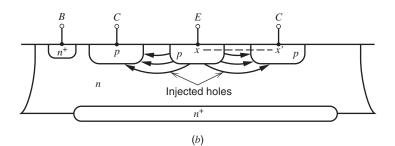

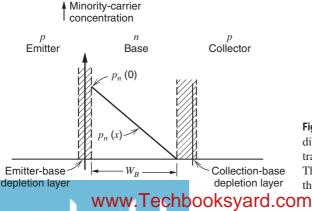

A cross section AA' is taken through the device of Fig. 1.6b and carrier concentrations along this section are plotted in Fig. 1.6c. Hole concentrations are denoted by p and electron concentrations by n with subscripts p or n representing p-type or n-type regions. The ntype emitter and collector regions are distinguished by subscripts E and C, respectively. The carrier concentrations shown in Fig. 1.6c apply to a device in the *forward-active region*. That is, the base-emitter junction is forward biased and the base-collector junction is reverse biased. The minority-carrier concentrations in the base at the edges of the depletion regions can be calculated from a Boltzmann approximation to the Fermi-Dirac distribution function to give<sup>6</sup>

$$n_p(0) = n_{po} \exp \frac{V_{BE}}{V_T} \tag{1.27}$$

$$n_p(W_B) = n_{po} \exp \frac{V_{BC}}{V_T} \simeq 0 \tag{1.28}$$

where  $W_B$  is the width of the base from the base-emitter depletion layer edge to the basecollector depletion layer edge and  $n_{po}$  is the equilibrium concentration of electrons in the base. Note that  $V_{BC}$  is negative for an *npn* transistor in the forward-active region and thus  $n_p(W_B)$  is very small. Low-level injection conditions are assumed in the derivation of (1.27) and (1.28). This means that the minority-carrier concentrations are always assumed much smaller than the majority-carrier concentration.

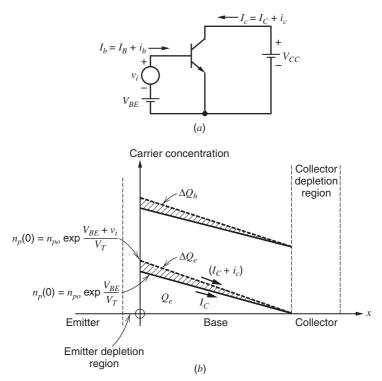

If *recombination* of holes and electrons in the base is small, it can be shown that<sup>7</sup> the minority-carrier concentration  $n_p(x)$  in the base varies *linearly* with distance. Thus a straight line can be drawn joining the concentrations at x = 0 and  $x = W_B$  in Fig. 1.6c.

For charge neutrality in the base, it is necessary that

$$N_A + n_p(x) = p_p(x)$$

(1.29)

and thus

$$p_p(x) - n_p(x) = N_A \tag{1.30}$$

where  $p_p(x)$  is the hole concentration in the base and  $N_A$  is the base doping density that is assumed constant. Equation 1.30 indicates that the hole and electron concentrations are separated by a constant amount and thus  $p_p(x)$  also varies linearly with distance.

Collector current is produced by minority-carrier electrons in the base diffusing in the direction of the concentration gradient and being swept across the collector-base depletion region by the field existing there. The diffusion current density due to electrons in the base is

$$J_n = q D_n \frac{dn_p(x)}{dx} \tag{1.31}$$

where  $D_n$  is the diffusion constant for electrons. From Fig. 1.6c

$$J_n = -qD_n \frac{n_p(0)}{W_B} \tag{1.32}$$

If  $I_C$  is the collector current and is taken as positive flowing *into* the collector, it follows from (1.32) that

$$I_C = qAD_n \frac{n_p(0)}{W_B} \tag{1.33}$$

#### 1.3 Large-Signal Behavior of Bipolar Transistors 11

where A is the cross-sectional area of the emitter. Substitution of (1.27) into (1.33) gives

$$I_C = \frac{qAD_n n_{po}}{W_B} \exp \frac{V_{BE}}{V_T}$$

(1.34)

$$= I_S \exp \frac{V_{BE}}{V_T} \tag{1.35}$$

where

$$I_S = \frac{qAD_n n_{po}}{W_B} \tag{1.36}$$

and  $I_S$  is a constant used to describe the transfer characteristic of the transistor in the forwardactive region. Equation 1.36 can be expressed in terms of the base doping density by noting that<sup>8</sup> (see Chapter 2)

$$n_{po} = \frac{n_i^2}{N_A} \tag{1.37}$$

and substitution of (1.37) in (1.36) gives

$$I_S = \frac{qAD_n n_i^2}{W_B N_A} = \frac{qA\overline{D}_n n_i^2}{Q_B}$$

(1.38)

where  $Q_B = W_B N_A$  is the number of doping atoms in the base per unit area of the emitter and  $n_i$  is the intrinsic carrier concentration in silicon. In this form (1.38) applies to both uniformand nonuniform-base transistors and  $D_n$  has been replaced by  $\overline{D}_n$ , which is an average effective value for the electron diffusion constant in the base. This is necessary for nonuniform-base devices because the diffusion constant is a function of impurity concentration. Typical values of  $I_S$  as given by (1.38) are from  $10^{-14}$  to  $10^{-16}$  A.

Equation 1.35 gives the collector current as a function of base-emitter voltage. The base current  $I_B$  is also an important parameter and, at moderate current levels, consists of two major components. One of these  $(I_{B1})$  represents recombination of holes and electrons in the base and is proportional to the minority-carrier charge  $Q_e$  in the base. From Fig. 1.6*c*, the minority-carrier charge in the base is

$$Q_e = \frac{1}{2} n_p(0) W_B q A \tag{1.39}$$

and we have

$$I_{B1} = \frac{Q_e}{\tau_b} = \frac{1}{2} \frac{n_p(0) W_B q A}{\tau_b}$$

(1.40)

where  $\tau_b$  is the minority-carrier lifetime in the base.  $I_{B1}$  represents a flow of majority holes from the base lead into the base region. Substitution of (1.27) in (1.40) gives

$$I_{B1} = \frac{1}{2} \frac{n_{po} W_B q A}{\tau_b} \exp \frac{V_{BE}}{V_T}$$

(1.41)

The second major component of base current (usually the dominant one in integratedcircuit npn devices) is due to injection of holes from the base into the emitter. This current component depends on the gradient of minority-carrier holes in the emitter and is<sup>9</sup>

$$I_{B2} = \frac{qAD_p}{L_p} p_{nE}(0)$$

(1.42)

where  $D_p$  is the diffusion constant for holes and  $L_p$  is the diffusion length (assumed small) for holes in the emitter.  $p_{nE}(0)$  is the concentration of holes in the emitter at the edge of the

#### 12 Chapter 1 Models for Integrated-Circuit Active Devices

depletion region and is

$$p_{nE}(0) = p_{nEo} \exp \frac{V_{BE}}{V_T}$$

(1.43)

If  $N_D$  is the donor atom concentration in the emitter (assumed constant), then

$$p_{nEo} \simeq \frac{n_i^2}{N_D} \tag{1.44}$$

The emitter is deliberately doped much more heavily than the base, making  $N_D$  large and  $p_{nEo}$  small, so that the base-current component,  $I_{B2}$ , is minimized.

Substitution of (1.43) and (1.44) in (1.42) gives

$$I_{B2} = \frac{qAD_p}{L_p} \frac{n_i^2}{N_D} \exp \frac{V_{BE}}{V_T}$$

(1.45)

The total base current,  $I_B$ , is the sum of  $I_{B1}$  and  $I_{B2}$ :

$$I_{B} = I_{B1} + I_{B2} = \left(\frac{1}{2}\frac{n_{po}W_{B}qA}{\tau_{b}} + \frac{qAD_{p}}{L_{p}}\frac{n_{i}^{2}}{N_{D}}\right) \exp\frac{V_{BE}}{V_{T}}$$

(1.46)

Although this equation was derived assuming uniform base and emitter doping, it gives the correct functional dependence of  $I_B$  on device parameters for practical double-diffused nonuniform-base devices. Second-order components of  $I_B$ , which are important at low current levels, are considered later.

Since  $I_C$  in (1.35) and  $I_B$  in (1.46) are both proportional to  $\exp(V_{BE}/V_T)$  in this analysis, the base current can be expressed in terms of collector current as

$$I_B = \frac{I_C}{\beta_F} \tag{1.47}$$

where  $\beta_F$  is the forward current gain. An expression for  $\beta_F$  can be calculated by substituting (1.34) and (1.46) in (1.47) to give

$$\beta_F = \frac{\frac{qAD_n n_{po}}{W_B}}{\frac{1}{2} \frac{n_{po} W_B qA}{\tau_b} + \frac{qAD_p n_i^2}{L_p N_D}} = \frac{1}{\frac{W_B^2}{2\tau_b D_n} + \frac{D_p}{D_n} \frac{W_B}{L_p} \frac{N_A}{N_D}}$$

(1.48)

where (1.37) has been substituted for  $n_{po}$ . Equation 1.48 shows that  $\beta_F$  is maximized by minimizing the base width  $W_B$  and maximizing the ratio of emitter to base doping densities  $N_D/N_A$ . Typical values of  $\beta_F$  for *npn* transistors in integrated circuits are 50 to 500, whereas lateral *pnp* transistors (to be described in Chapter 2) have values 10 to 100. Finally, the emitter current is

$$I_E = -(I_C + I_B) = -\left(I_C + \frac{I_C}{\beta_F}\right) = -\frac{I_C}{\alpha_F}$$

(1.49)

where

$$\alpha_F = \frac{\beta_F}{1 + \beta_F}$$

(1.50)

www.Techbooksyard.com

#### 1.3 Large-Signal Behavior of Bipolar Transistors 13

The value of  $\alpha_F$  can be expressed in terms of device parameters by substituting (1.48) in (1.50) to obtain

$$\alpha_F = \frac{1}{1 + \frac{1}{\beta_F}} = \frac{1}{1 + \frac{W_B^2}{2\tau_b D_n} + \frac{D_p}{D_n} \frac{W_B}{L_p} \frac{N_A}{N_D}} \simeq \alpha_T \gamma$$

(1.51)

where

$$\alpha_T = \frac{1}{1 + \frac{W_B^2}{2\tau_b D_n}}$$

(1.51a)

$$\gamma = \frac{1}{1 + \frac{D_p}{D_n} \frac{W_B}{L_p} \frac{N_A}{N_D}}$$

(1.51b)

The validity of (1.51) depends on  $W_B^2/2 \tau_b D_n \ll 1$  and  $(D_p/D_n)(W_B/L_p)(N_A/N_D) \ll 1$ , and this is always true if  $\beta_F$  is large [see (1.48)]. The term  $\gamma$  in (1.51) is called the *emitter injection efficiency* and is equal to the ratio of the electron current (*npn* transistor) injected into the base from the emitter to the total hole and electron current crossing the base-emitter junction. Ideally  $\gamma \rightarrow 1$ , and this is achieved by making  $N_D/N_A$  large and  $W_B$  small. In that case very little reverse injection occurs from base to emitter.

The term  $\alpha_T$  in (1.51) is called the *base transport factor* and represents the fraction of carriers injected into the base (from the emitter) that reach the collector. Ideally  $\alpha_T \rightarrow 1$  and this is achieved by making  $W_B$  small. It is evident from the above development that fabrication changes that cause  $\alpha_T$  and  $\gamma$  to approach unity also maximize the value of  $\beta_F$  of the transistor.

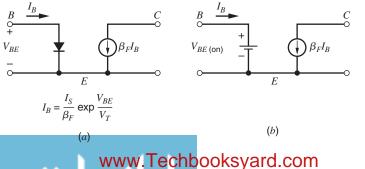

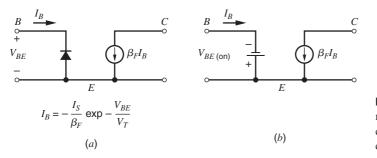

The results derived above allow formulation of a large-signal model of the transistor suitable for bias-circuit calculations with devices in the forward-active region. One such circuit is shown in Fig. 1.7 and consists of a base-emitter diode to model (1.46) and a controlled collector-current generator to model (1.47). Note that the collector voltage ideally has no influence on the collector current and the collector node acts as a high-impedance current source. A simpler version of this equivalent circuit, which is often useful, is shown in Fig. 1.7*b*, where the input diode has been replaced by a battery with a value  $V_{BE(on)}$ , which is usually 0.6 to 0.7 V. This represents the fact that in the forward-active region the base-emitter voltage varies very little because of the steep slope of the exponential characteristic. In some circuits the temperature coefficient of  $V_{BE(on)}$  is important, and a typical value for this is  $-2 \text{ mV}/^{\circ}\text{C}$ . The equivalent circuits are shown in Fig. 1.8.

Figure 1.7 Large-signal models of *npn* transistors for use in bias calculations. (*a*) Circuit incorporating an input diode. (*b*) Simplified circuit with

an input voltage source.

Figure 1.8 Large-signal models of *pnp* transistors corresponding to the circuits of Fig. 1.7.

## 1.3.2 Effects of Collector Voltage on Large-Signal Characteristics in the Forward-Active Region

In the analysis of the previous section, the collector-base junction was assumed reverse biased and ideally had no effect on the collector currents. This is a useful approximation for firstorder calculations, but is not strictly true in practice. There are occasions when the influence of collector voltage on collector current is important, and this will now be investigated.

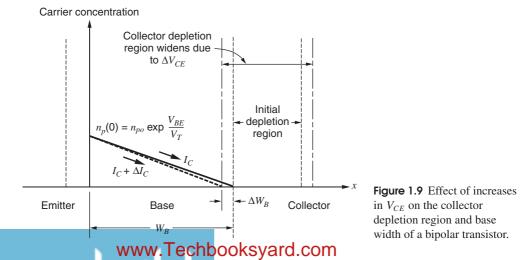

The collector voltage has a dramatic effect on the collector current in two regions of device operation. These are the saturation ( $V_{CE}$  approaches zero) and breakdown ( $V_{CE}$  very large) regions that will be considered later. For values of collector-emitter voltage  $V_{CE}$  between these extremes, the collector current increases slowly as  $V_{CE}$  increases. The reason for this can be seen from Fig. 1.9, which is a sketch of the minority-carrier concentration in the base of the transistor. Consider the effect of changes in  $V_{CE}$  on the carrier concentration for constant  $V_{BE}$ . Since  $V_{BE}$  is constant, the change in  $V_{CB}$  equals the change in  $V_{CE}$  and this causes an increase in the collector-base depletion-layer width as shown. The change in the base width of the transistor,  $\Delta W_B$ , equals the change in the depletion-layer width and causes an increase  $\Delta I_C$ in the collector current.

From (1.35) and (1.38) we have

$$I_C = \frac{qA\overline{D}_n n_i^2}{Q_B} \exp \frac{V_{BE}}{V_T}$$

(1.52)

Differentiation of (1.52) yields

$$\frac{\partial I_C}{\partial V_{CE}} = -\frac{qA\overline{D}_n n_i^2}{Q_B^2} \left(\exp\frac{V_{BE}}{V_T}\right) \frac{dQ_B}{dV_{CE}}$$

(1.53)

and substitution of (1.52) in (1.53) gives

$$\frac{\partial I_C}{\partial V_{CE}} = -\frac{I_C}{Q_B} \frac{dQ_B}{dV_{CE}} \tag{1.54}$$

For a uniform-base transistor  $Q_B = W_B N_A$ , and (1.54) becomes

$$\frac{\partial I_C}{\partial V_{CE}} = -\frac{I_C}{W_B} \frac{dW_B}{dV_{CE}} \tag{1.55}$$

Note that since the base width *decreases* as  $V_{CE}$  increases,  $dW_B/dV_{CE}$  in (1.55) is negative and thus  $\partial I_C/\partial V_{CE}$  is positive. The magnitude of  $dW_B/dV_{CE}$  can be calculated from (1.18) for a uniform-base transistor. This equation predicts that  $dW_B/dV_{CE}$  is a function of the bias value of  $V_{CE}$ , but the variation is typically small for a reverse-biased junction and  $dW_B/dV_{CE}$  is often assumed constant. The resulting predictions agree adequately with experimental results.

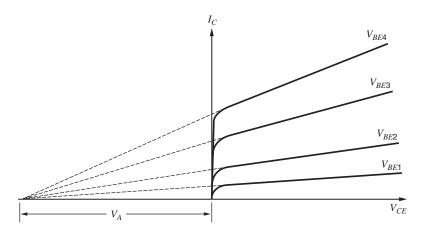

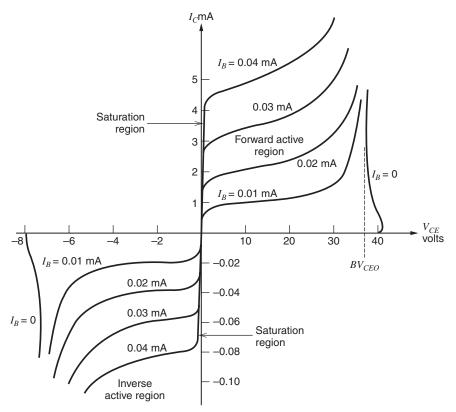

Equation 1.55 shows that  $\partial I_C / \partial V_{CE}$  is proportional to the collector-bias current and inversely proportional to the transistor base width. Thus narrow-base transistors show a greater dependence of  $I_C$  on  $V_{CE}$  in the forward-active region. The dependence of  $\partial I_C / \partial V_{CE}$  on  $I_C$ results in typical transistor output characteristics as shown in Fig. 1.10. In accordance with the assumptions made in the foregoing analysis, these characteristics are shown for constant values of  $V_{BE}$ . However, in most integrated-circuit transistors the base current is dependent only on  $V_{BE}$  and not on  $V_{CE}$ , and thus constant-base-current characteristics can often be used in the following calculation. The reason for this is that the base current is usually dominated by the  $I_{B2}$  component of (1.45), which has no dependence on  $V_{CE}$ . Extrapolation of the characteristics of Fig. 1.10 back to the  $V_{CE}$  axis gives an intercept  $V_A$  called the Early voltage, where

#### 16 Chapter 1 Models for Integrated-Circuit Active Devices

Substitution of (1.55) in (1.56) gives

$$V_A = -W_B \frac{dV_{CE}}{dW_B} \tag{1.57}$$

which is a constant, independent of  $I_C$ . Thus all the characteristics extrapolate to the same point on the  $V_{CE}$  axis. The variation of  $I_C$  with  $V_{CE}$  is called the Early effect, and  $V_A$  is a common model parameter for circuit-analysis computer programs. Typical values of  $V_A$ for integrated-circuit transistors are 15 to 100 V. The inclusion of Early effect in dc bias calculations is usually limited to computer analysis because of the complexity introduced into the calculation. However, the influence of the Early effect is often dominant in small-signal calculations for high-gain circuits and this point will be considered later.

Finally, the influence of Early effect on the transistor large-signal characteristics in the forward-active region can be represented approximately by modifying (1.35) to

$$I_C = I_S \left( 1 + \frac{V_{CE}}{V_A} \right) \exp \frac{V_{BE}}{V_T}$$

(1.58)

This is a common means of representing the device output characteristics for computer simulation.

#### 1.3.3 Saturation and Inverse-Active Regions

Saturation is a region of device operation that is usually avoided in analog circuits because the transistor gain is very low in this region. Saturation is much more commonly encountered in digital circuits, where it provides a well-specified output voltage that represents a logic state.

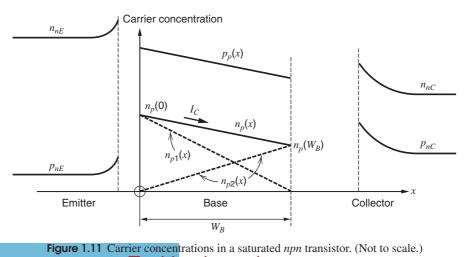

In saturation, both emitter-base and collector-base junctions are forward biased. Consequently, the collector-emitter voltage  $V_{CE}$  is quite small and is usually in the range 0.05 to 0.3 V. The carrier concentrations in a saturated *npn* transistor with uniform base doping are shown in Fig. 1.11. The minority-carrier concentration in the base at the edge of the depletion region is again given by (1.28) as

$$n_p(W_B) = n_{po} \exp \frac{V_{BC}}{V_T}$$

(1.59)

Figure 1.12 Typical  $I_C$ - $V_{CE}$  characteristics for an *npn* bipolar transistor. Note the different scales for positive and negative currents and voltages.

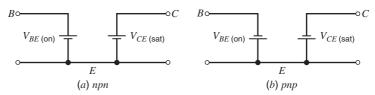

but since  $V_{BC}$  is now positive, the value of  $n_p(W_B)$  is no longer negligible. Consequently, changes in  $V_{CE}$  with  $V_{BE}$  held constant (which cause equal changes in  $V_{BC}$ ) directly affect  $n_p(W_B)$ . Since the collector current is proportional to the slope of the minority-carrier concentration in the base [see (1.31)], it is also proportional to  $[n_p(0) - n_p(W_B)]$  from Fig. 1.11. Thus changes in  $n_p(W_B)$  directly affect the collector current, and the collector node of the transistor appears to have a *low impedance*. As  $V_{CE}$  is decreased in saturation with  $V_{BE}$  held constant,  $V_{BC}$  increases, as does  $n_p(W_B)$  from (1.59). Thus, from Fig. 1.11, the collector current decreases because the slope of the carrier concentration decreases. This gives rise to the saturation region of the  $I_C - V_{CE}$  characteristic shown in Fig. 1.12. The slope of the  $I_C - V_{CE}$  characteristic in this region is largely determined by the resistance in series with the collector lead due to the finite resistivity of the *n*-type collector material. A useful model for the transistor in this region is shown in Fig. 1.13 and consists of a fixed voltage source to represent  $V_{BE(on)}$ , and a fixed voltage source to represent the collector-emitter voltage  $V_{CE(sat)}$ . A more accurate but more complex model includes a resistor in series with the collector. This resistor can have a value ranging from 20 to 500  $\Omega$ , depending on the device structure.

An additional aspect of transistor behavior in the saturation region is apparent from Fig. 1.11. For a given collector current, there is now a much larger amount of stored charge in the base than there is in the forward-active region. Thus the base-current contribution represented by (1.41) will be larger in saturation. In addition, since the collector-base junction is now forward biased, there is a new base-current component due to injection of carriers from the

Figure 1.13 Large-signal models for bipolar transistors in the saturation region.

base to the collector. These two effects result in a base current  $I_B$  in saturation, which is larger than in the forward-active region for a given collector current  $I_C$ . Ratio  $I_C/I_B$  in saturation is often referred to as the *forced*  $\beta$  and is always less than  $\beta_F$ . As the forced  $\beta$  is made lower with respect to  $\beta_F$ , the device is said to be more *heavily saturated*.

The minority-carrier concentration in saturation shown in Fig. 1.11 is a straight line joining the two end points, assuming that recombination is small. This can be represented as a linear superposition of the two dotted distributions as shown. The justification for this is that the terminal currents depend *linearly* on the concentrations  $n_p(0)$  and  $n_p(W_B)$ . This picture of device carrier concentrations can be used to derive some general equations describing transistor behavior. Each of the distributions in Fig. 1.11 is considered separately and the two contributions are combined. The *emitter* current that would result from  $n_{p1}(x)$  above is given by the classical diode equation

$$I_{EF} = -I_{ES} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) \tag{1.60}$$

where  $I_{ES}$  is a constant that is often referred to as the *saturation current* of the junction (no connection with the transistor saturation previously described). Equation 1.60 predicts that the junction current is given by  $I_{EF} \simeq I_{ES}$  with a reverse-bias voltage applied. However, in practice (1.60) is applicable only in the forward-bias region, since second-order effects dominate under reverse-bias conditions and typically result in a junction current several orders of magnitude larger than  $I_{ES}$ . The junction current that flows under reverse-bias conditions is often called the *leakage current* of the junction.

Returning to Fig. 1.11, we can describe the *collector* current resulting from  $n_{p2}(x)$  alone as

$$I_{CR} = -I_{CS} \left( \exp \frac{V_{BC}}{V_T} - 1 \right) \tag{1.61}$$

where  $I_{CS}$  is a constant. The total collector current  $I_C$  is given by  $I_{CR}$  plus the fraction of  $I_{EF}$  that reaches the collector (allowing for recombination and reverse emitter injection). Thus

$$I_C = \alpha_F I_{ES} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) - I_{CS} \left( \exp \frac{V_{BC}}{V_T} - 1 \right)$$

(1.62)

where  $\alpha_F$  has been defined previously by (1.51). Similarly, the total emitter current is composed of  $I_{EF}$  plus the fraction of  $I_{CR}$  that reaches the emitter with the transistor acting in an inverted mode. Thus

$$I_E = -I_{ES} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) + \alpha_R I_{CS} \left( \exp \frac{V_{BC}}{V_T} - 1 \right)$$

(1.63)

where  $\alpha_R$  is the ratio of emitter to collector current with the transistor operating *inverted* (i.e., with the collector-base junction forward biased and emitting carriers into the base and the emitter-base junction reverse biased and collecting carriers). Typical values of  $\alpha_R$  are 0.5 to 0.8.

An inverse current gain  $\beta_R$  is also defined

$$\beta_R = \frac{\alpha_R}{1 - \alpha_R} \tag{1.64}$$

and has typical values 1 to 5. This is the current gain of the transistor when operated inverted and is much lower than  $\beta_F$  because the device geometry and doping densities are designed to maximize  $\beta_F$ . The inverse-active region of device operation occurs for  $V_{CE}$  negative in an npn transistor and is shown in Fig. 1.12. In order to display these characteristics adequately in the same figure as the forward-active region, the negative voltage and current scales have been expanded. The inverse-active mode of operation is rarely encountered in analog circuits.

Equations 1.62 and 1.63 describe npn transistor operation in the saturation region when  $V_{BE}$  and  $V_{BC}$  are both positive, and also in the forward-active and inverse-active regions. These equations are the Ebers-Moll equations. In the forward-active region, they degenerate into a form similar to that of (1.35), (1.47), and (1.49) derived earlier. This can be shown by putting  $V_{BE}$  positive and  $V_{BC}$  negative in (1.62) and (1.63) to obtain

$$I_C = \alpha_F I_{ES} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) + I_{CS}$$

(1.65)

$$I_E = -I_{ES} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) - \alpha_R I_{CS}$$

(1.66)

Equation 1.65 is similar in form to (1.35) except that leakage currents that were previously neglected have now been included. This minor difference is significant only at high temperatures or very low operating currents. Comparison of (1.65) with (1.35) allows us to identify  $I_S = \alpha_F I_{ES}$ , and it can be shown<sup>10</sup> in general that

$$\alpha_F I_{ES} = \alpha_R I_{CS} = I_S \tag{1.67}$$

where this expression represents a reciprocity condition. Use of (1.67) in (1.62) and (1.63)allows the Ebers-Moll equations to be expressed in the general form

$$I_C = I_S \left( \exp \frac{V_{BE}}{V_T} - 1 \right) - \frac{I_S}{\alpha_R} \left( \exp \frac{V_{BC}}{V_T} - 1 \right)$$

(1.62a)

$$I_E = -\frac{I_S}{\alpha_F} \left( \exp \frac{V_{BE}}{V_T} - 1 \right) + I_S \left( \exp \frac{V_{BC}}{V_T} - 1 \right)$$

(1.63a)

This form is often used for computer representation of transistor large-signal behavior.

The effect of leakage currents mentioned above can be further illustrated as follows. In the forward-active region, from (1.66)

$$I_{ES}\left(\exp\frac{V_{BE}}{V_T} - 1\right) = -I_E - \alpha_R I_{CS}$$

(1.68)

Substitution of (1.68) in (1.65) gives

$$I_C = -\alpha_F I_E + I_{CO} \tag{1.69}$$

where

$$I_{CO} = I_{CS}(1 - \alpha_R \alpha_F) \tag{1.69a}$$

and  $I_{CO}$  is the collector-base leakage current with the emitter open. Although  $I_{CO}$  is given theoretically by (1.69a), in practice, surface leakage effects dominate when the collector-base junction is reverse biased and  $I_{CO}$  is typically several orders of magnitude larger than the value

#### 20 Chapter 1 Models for Integrated-Circuit Active Devices

given by (1.69a). However, (1.69) is still valid if the appropriate measured value for  $I_{CO}$  is used. Typical values of  $I_{CO}$  are from  $10^{-10}$  to  $10^{-12}$  A at 25°C, and the magnitude doubles about every 8°C. As a consequence, these leakage terms can become very significant at high temperatures. For example, consider the base current  $I_B$ . From Fig. 1.5 this is

$$I_B = -(I_C + I_E) (1.70)$$

If  $I_E$  is calculated from (1.69) and substituted in (1.70), the result is

$$I_B = \frac{1 - \alpha_F}{\alpha_F} I_C - \frac{I_{CO}}{\alpha_F} \tag{1.71}$$

But from (1.50)

$$\beta_F = \frac{\alpha_F}{1 - \alpha_F} \tag{1.72}$$

and use of (1.72) in (1.71) gives

$$I_B = \frac{I_C}{\beta_F} - \frac{I_{CO}}{\alpha_F} \tag{1.73}$$

Since the two terms in (1.73) have opposite signs, the effect of  $I_{CO}$  is to *decrease* the magnitude of the external base current at a given value of collector current.

#### EXAMPLE

If  $I_{CO}$  is  $10^{-10}$  A at 24°C, estimate its value at 120°C.

Assuming that  $I_{CO}$  doubles every 8°C, we have

$$I_{CO}(120^{\circ}\text{C}) = 10^{-10} \times 2^{12}$$

= 0.4 µA

### 1.3.4 Transistor Breakdown Voltages

In Section 1.2.2 the mechanism of avalanche breakdown in a *pn* junction was described. Similar effects occur at the base-emitter and base-collector junctions of a transistor and these effects limit the maximum voltages that can be applied to the device.

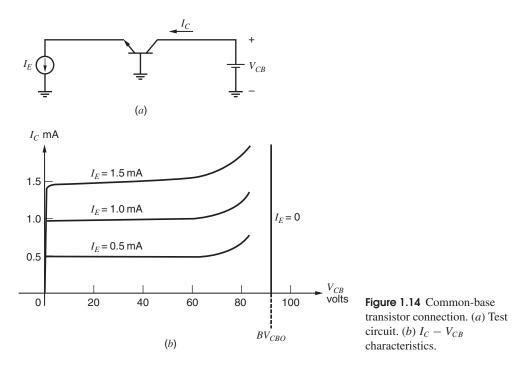

First consider a transistor in the common-base configuration shown in Fig. 1.14*a* and supplied with a constant emitter current. Typical  $I_C - V_{CB}$  characteristics for an *npn* transistor in such a connection are shown in Fig. 1.14*b*. For  $I_E = 0$  the collector-base junction breaks down at a voltage  $BV_{CBO}$ , which represents collector-base breakdown with the emitter open. For finite values of  $I_E$ , the effects of avalanche multiplication are apparent for values of  $V_{CB}$ below  $BV_{CBO}$ . In the example shown, the effective common-base current gain  $\alpha_F = I_C/I_E$ becomes larger than unity for values of  $V_{CB}$  above about 60 V. Operation in this region (but below  $BV_{CBO}$ ) can, however, be safely undertaken if the device power dissipation is not excessive. The considerations of Section 1.2.2 apply to this situation, and neglecting leakage currents, we can calculate the collector current in Fig. 1.14*a* as

$$I_C = -\alpha_F I_E M \tag{1.74}$$

where M is defined by (1.26) and thus

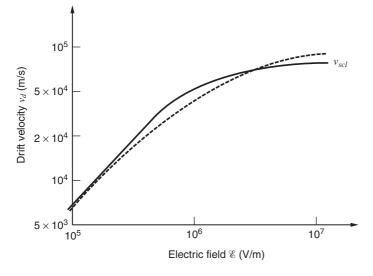

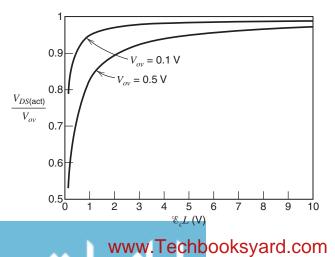

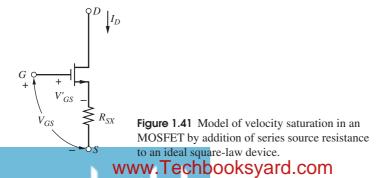

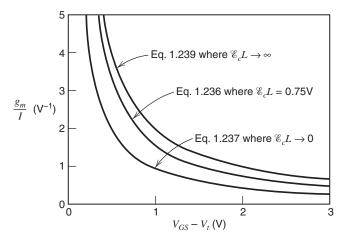

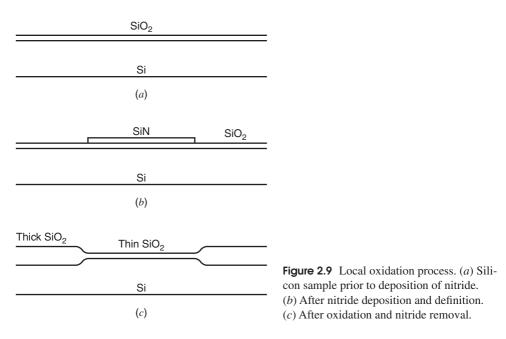

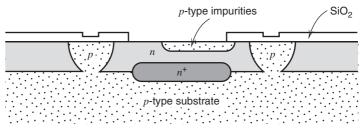

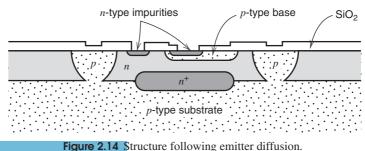

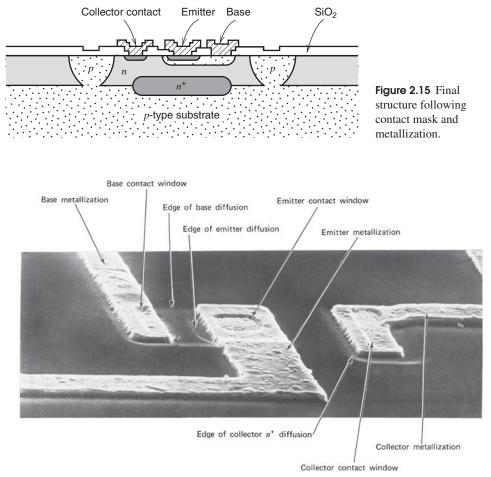

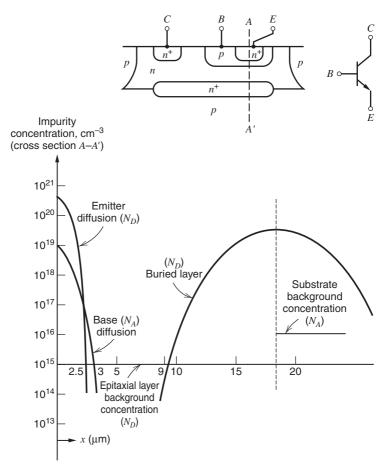

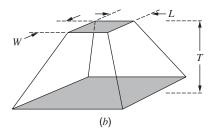

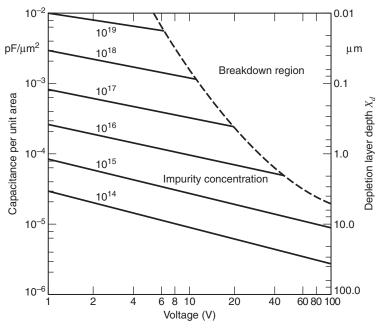

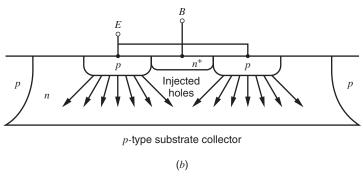

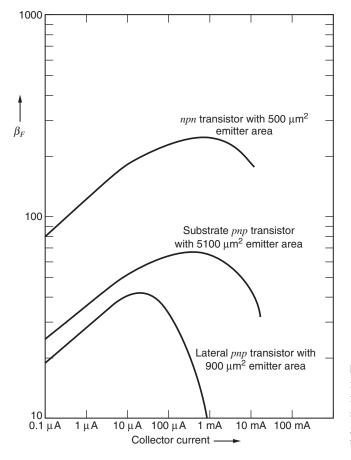

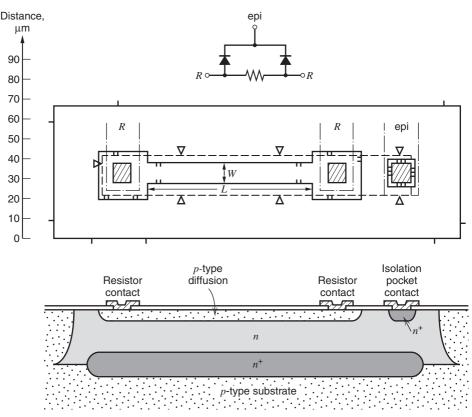

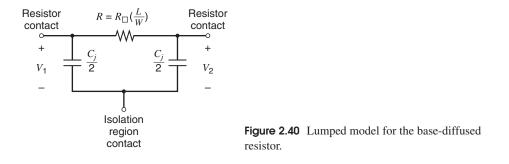

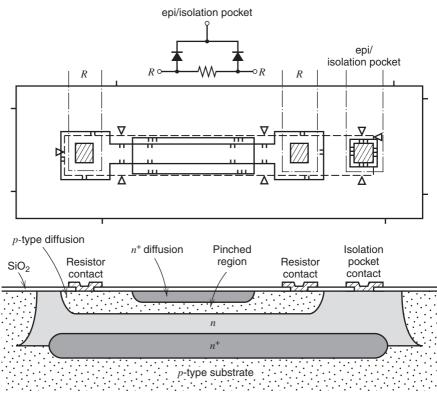

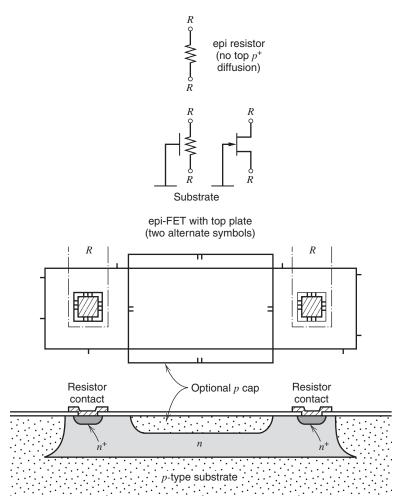

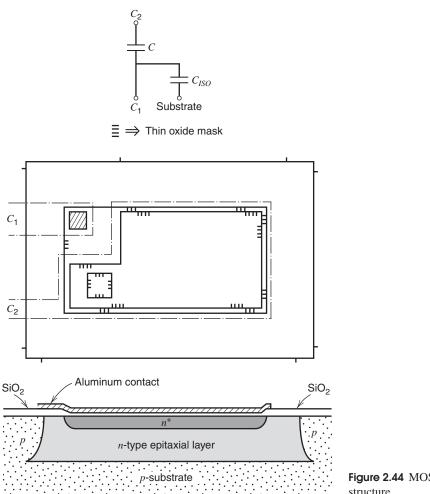

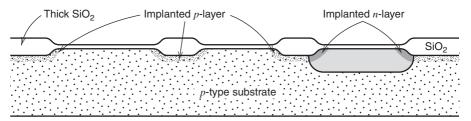

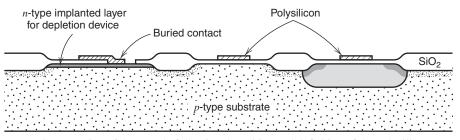

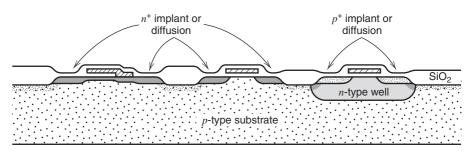

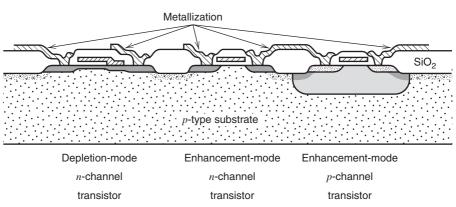

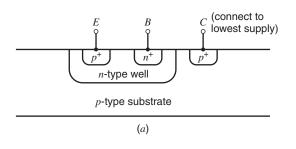

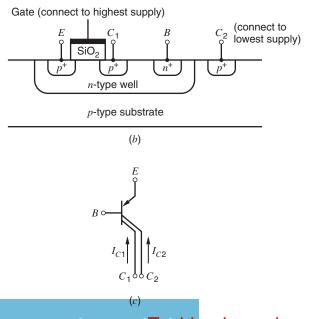

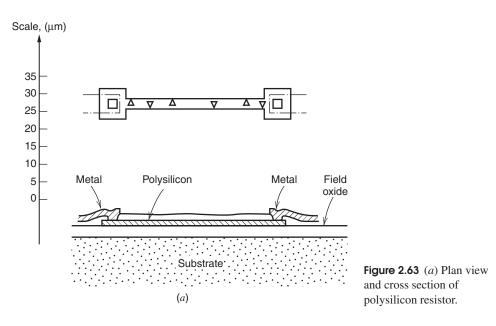

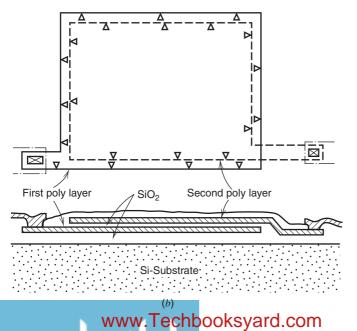

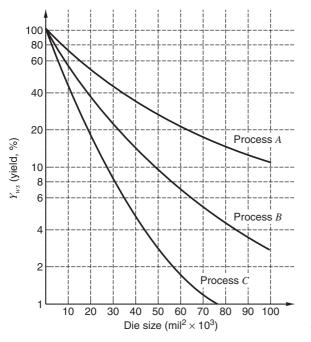

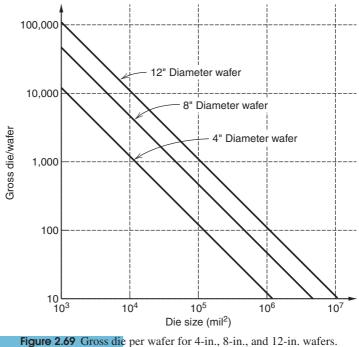

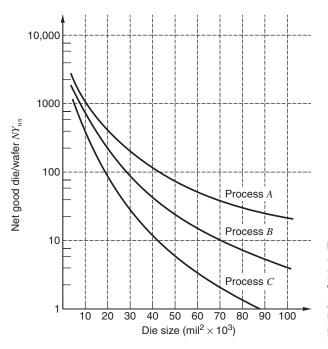

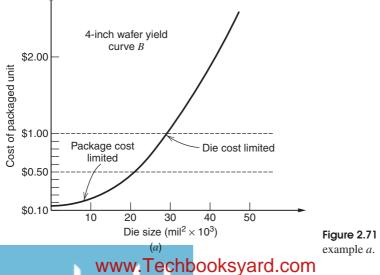

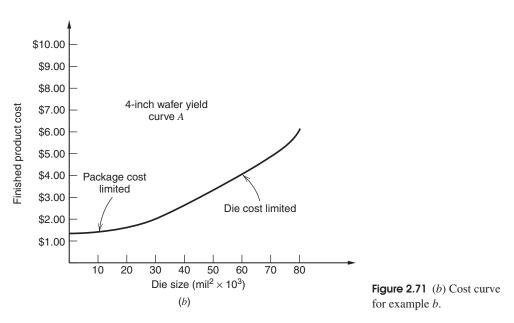

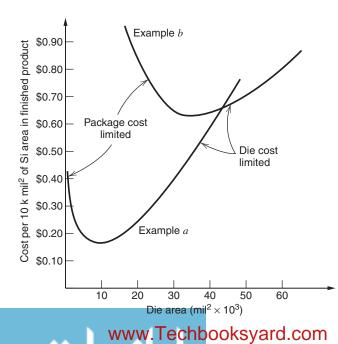

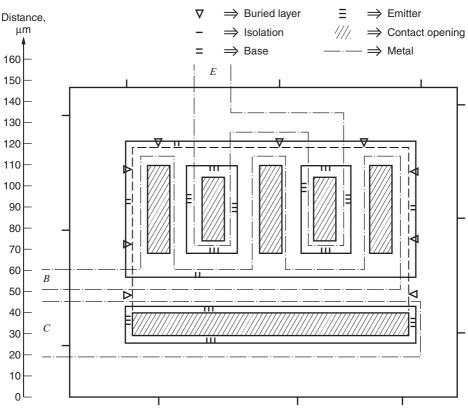

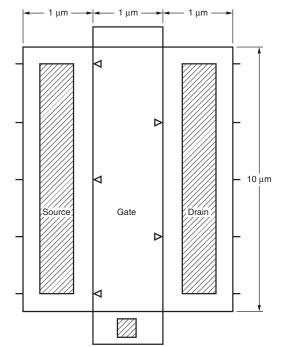

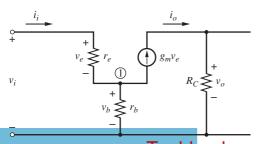

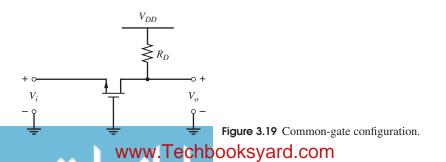

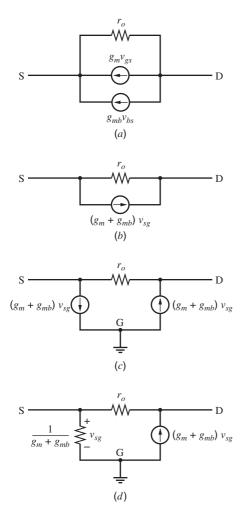

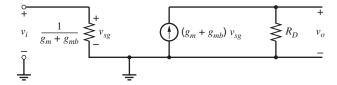

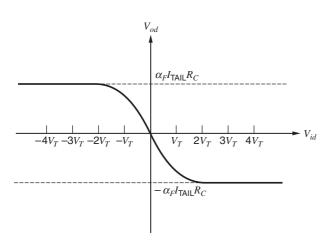

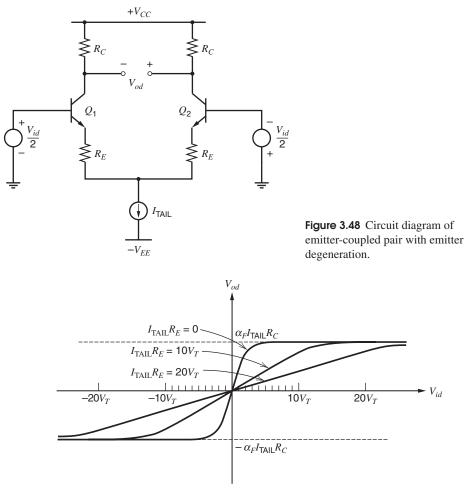

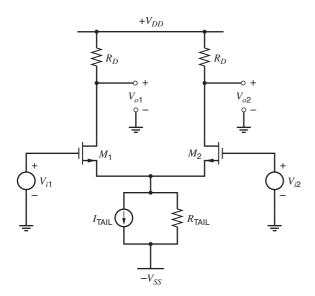

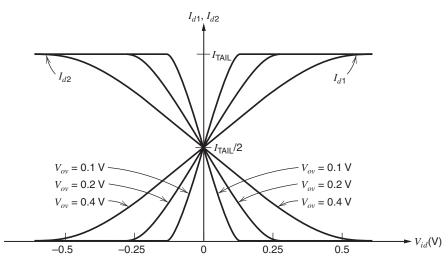

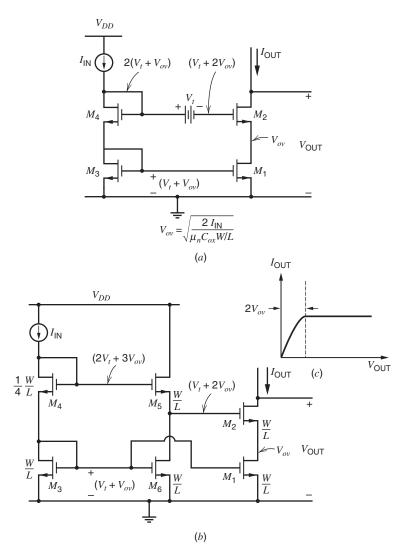

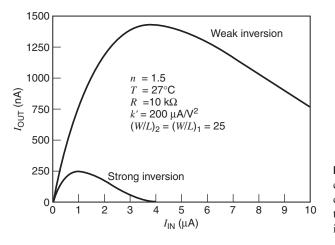

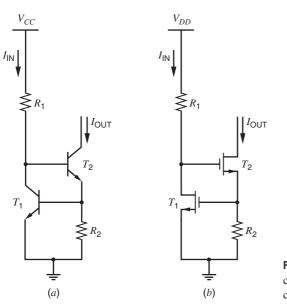

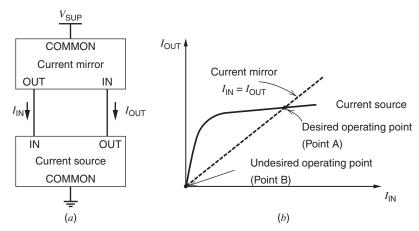

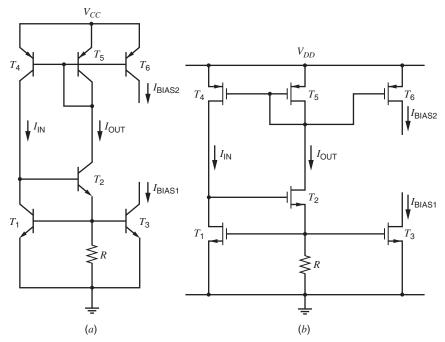

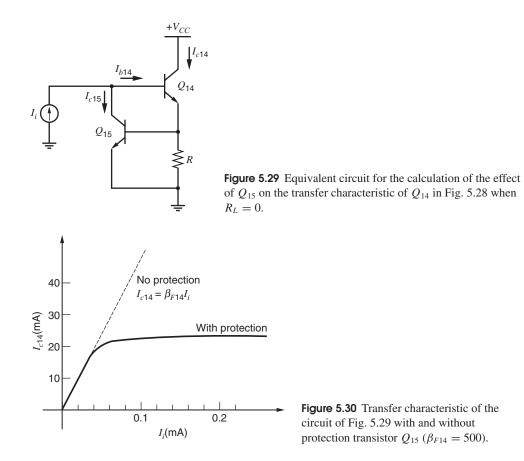

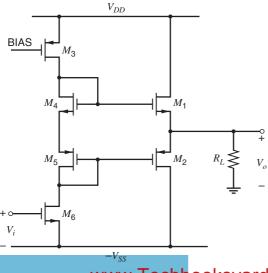

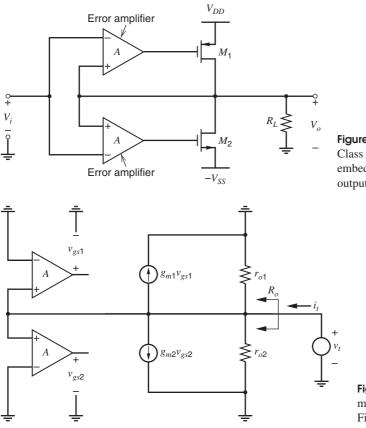

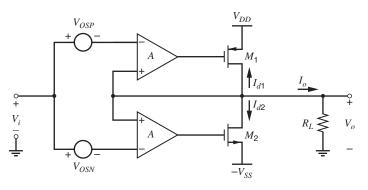

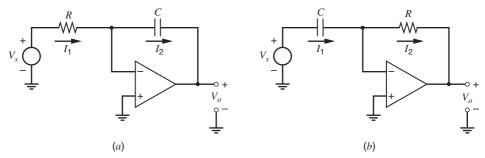

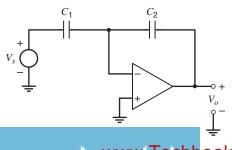

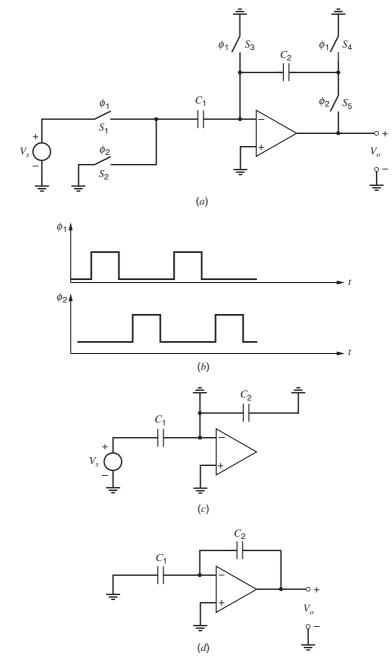

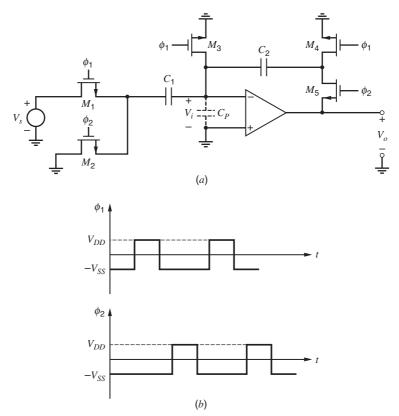

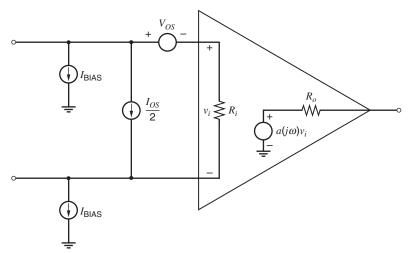

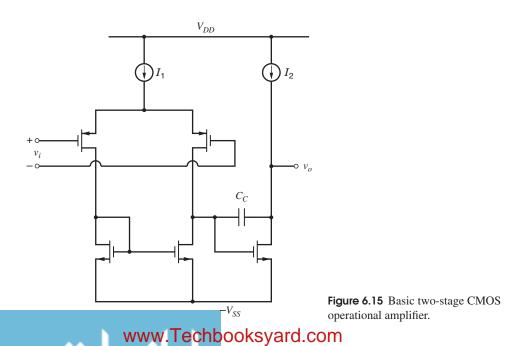

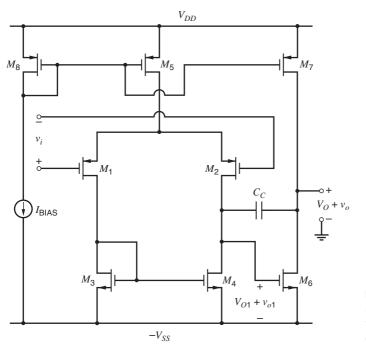

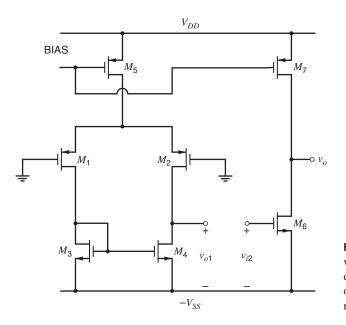

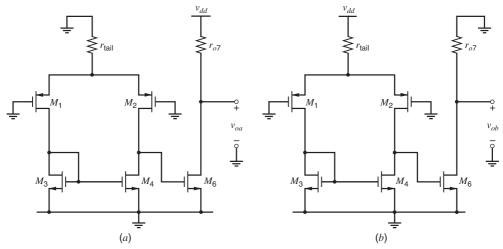

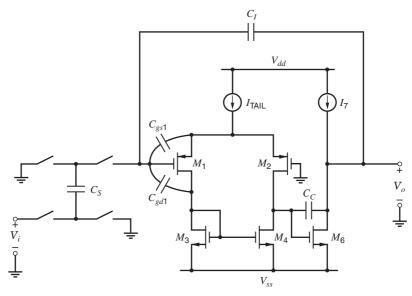

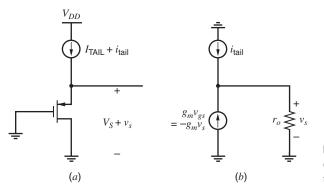

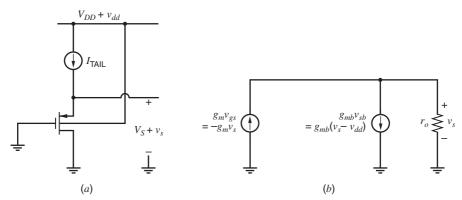

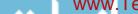

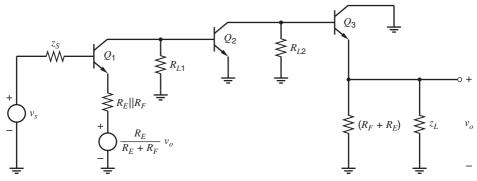

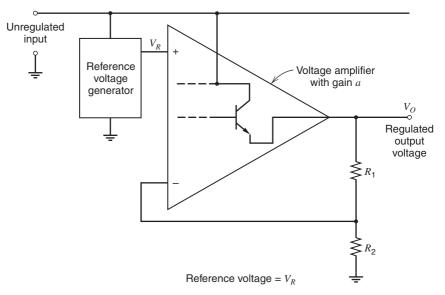

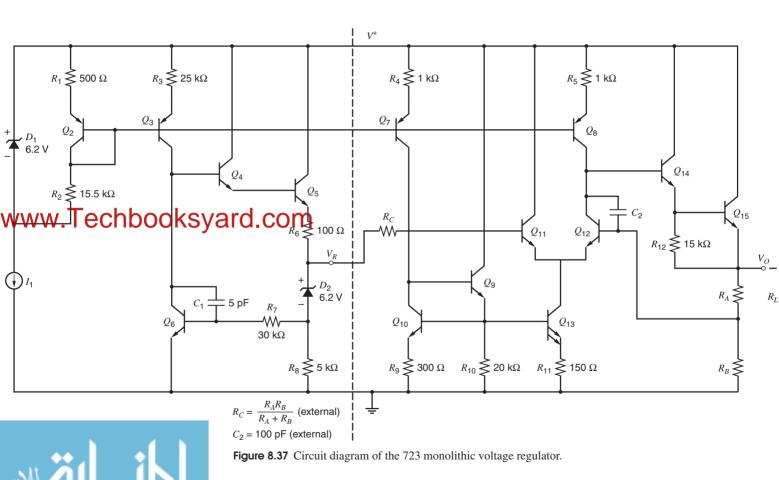

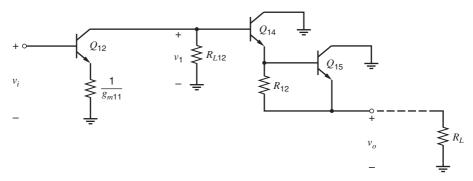

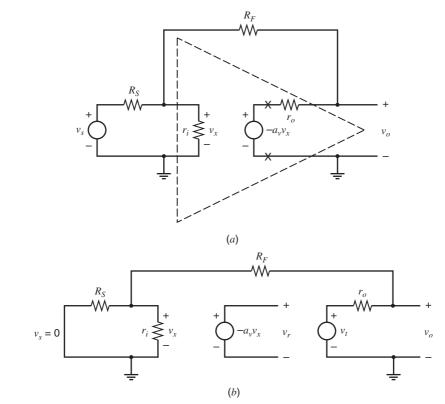

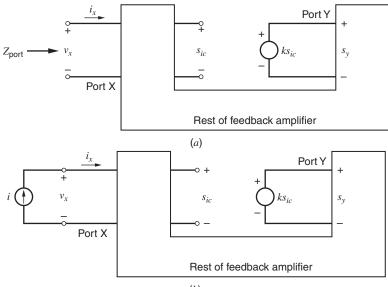

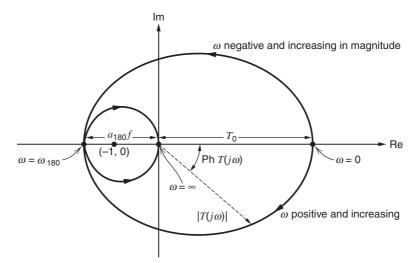

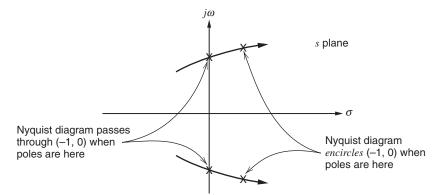

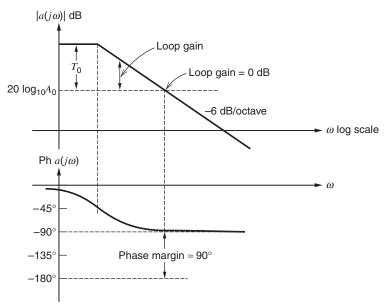

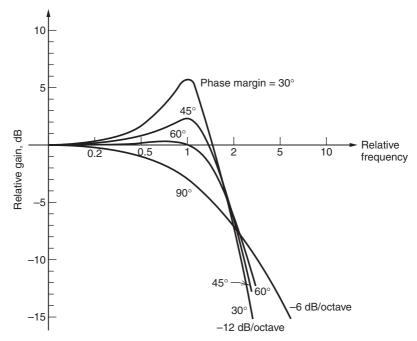

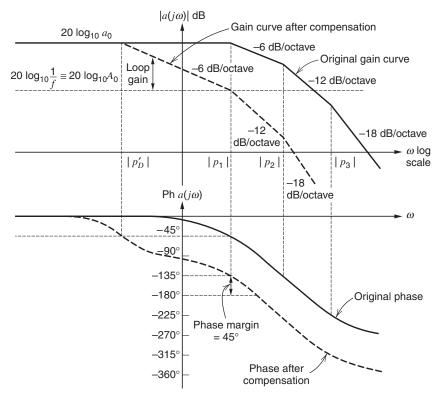

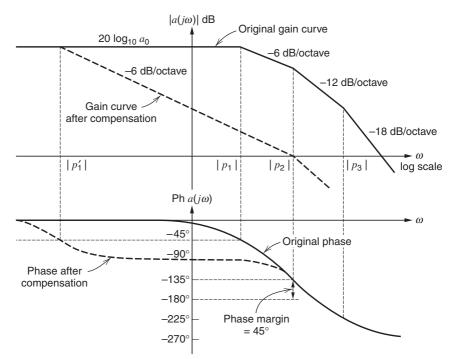

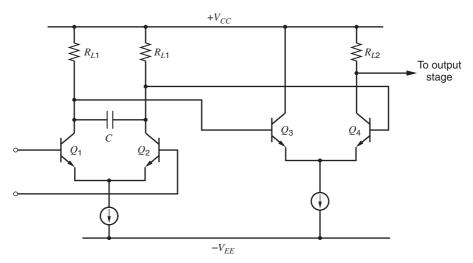

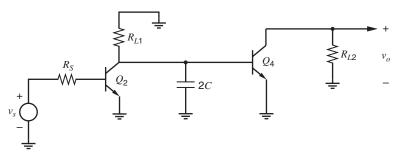

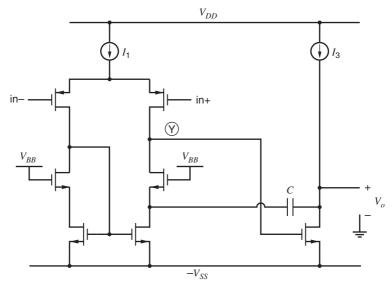

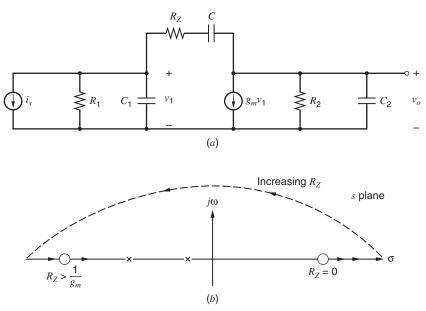

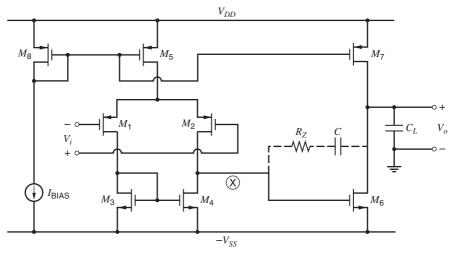

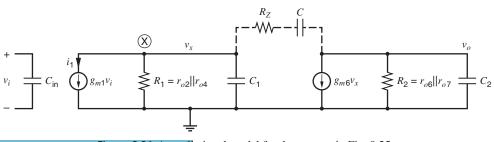

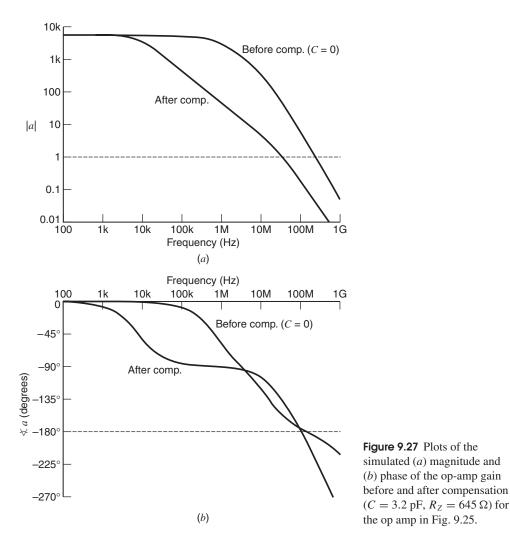

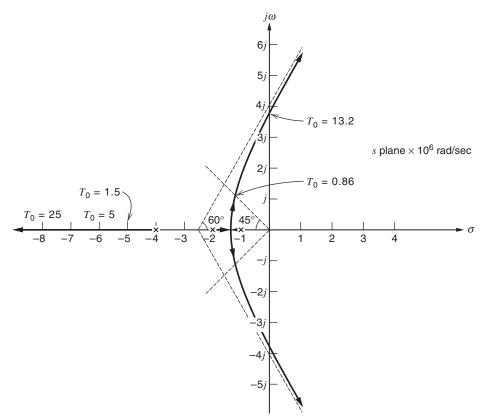

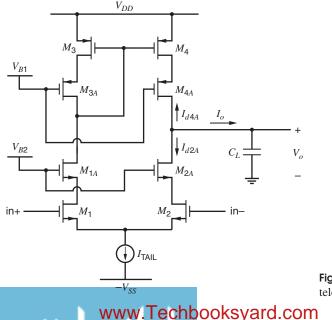

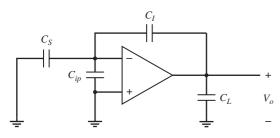

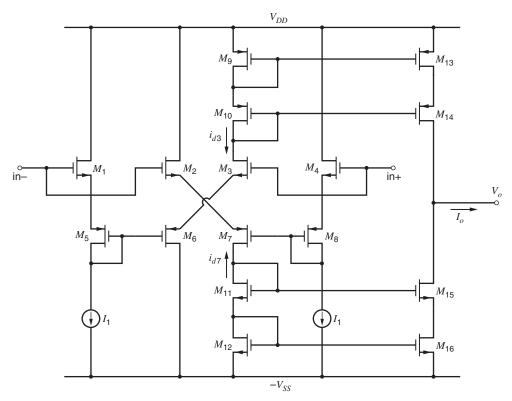

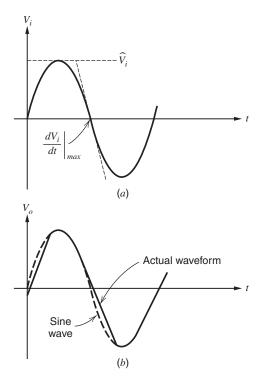

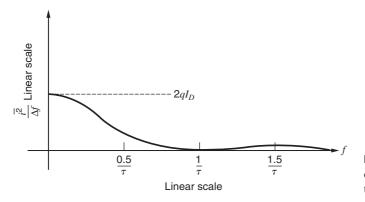

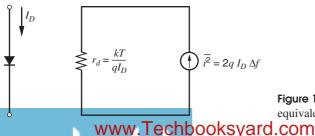

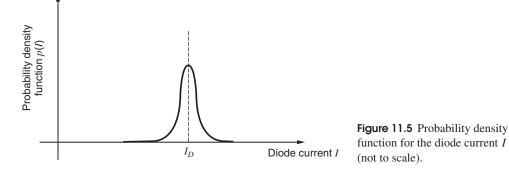

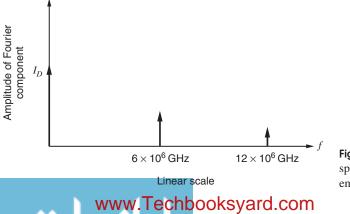

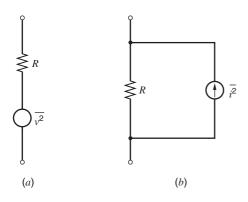

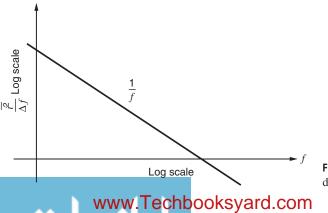

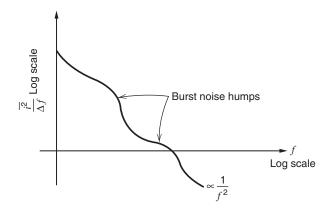

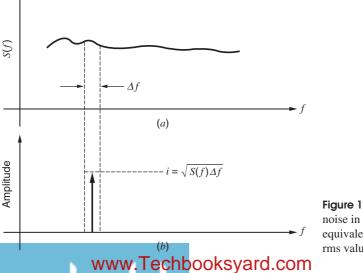

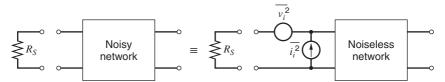

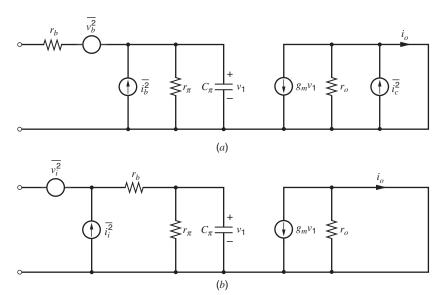

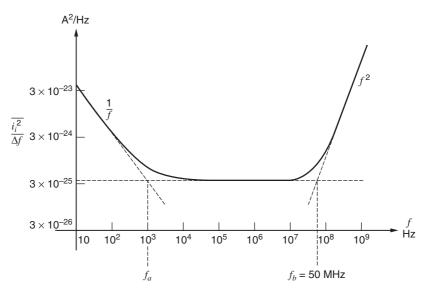

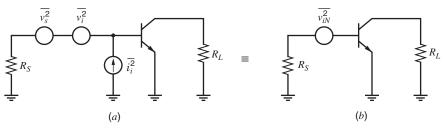

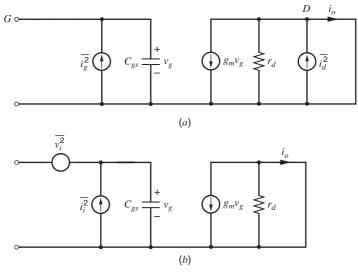

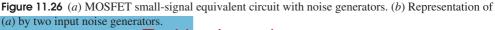

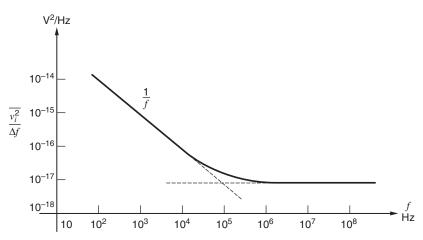

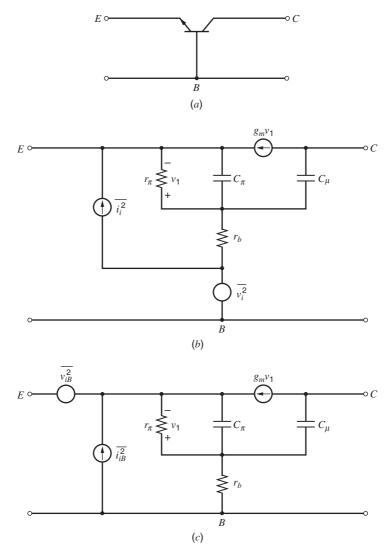

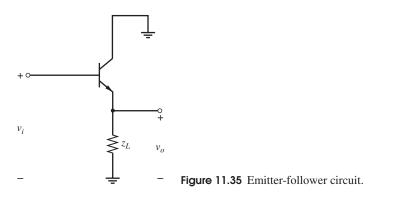

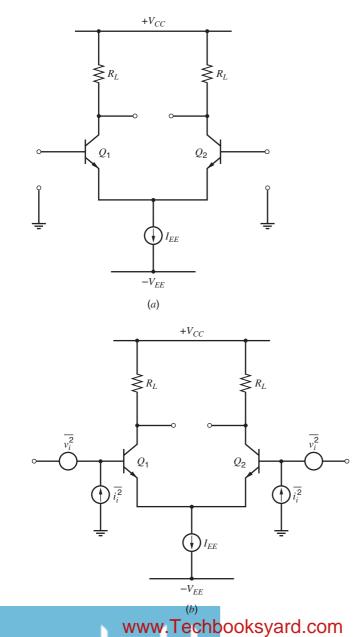

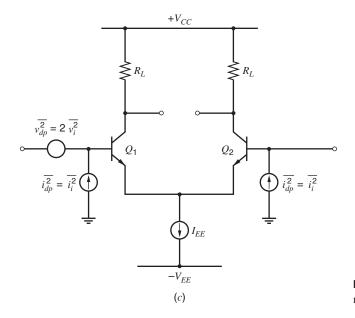

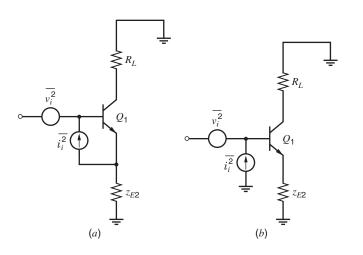

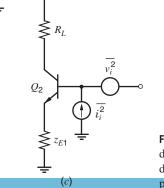

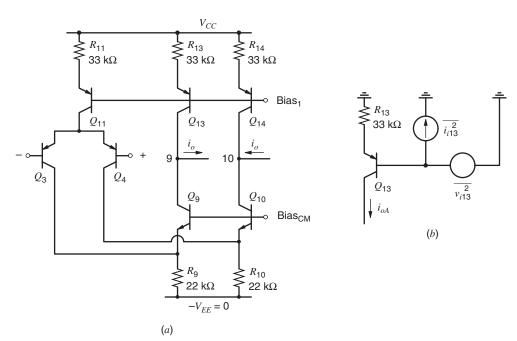

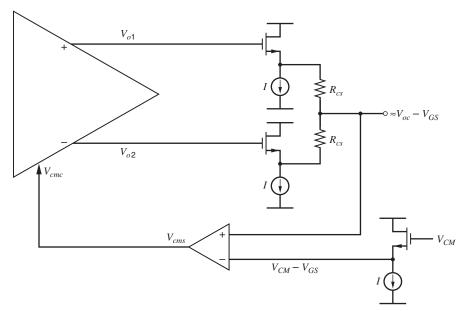

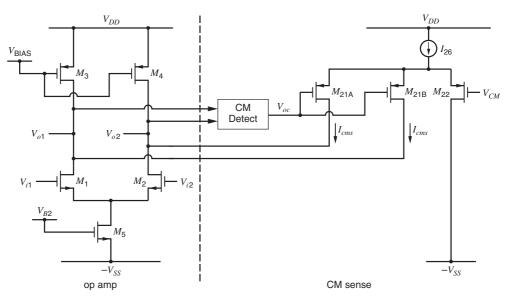

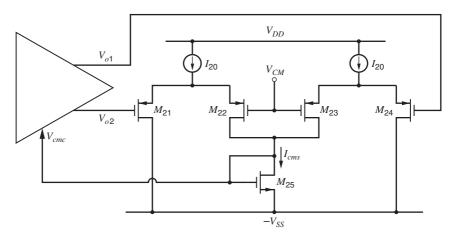

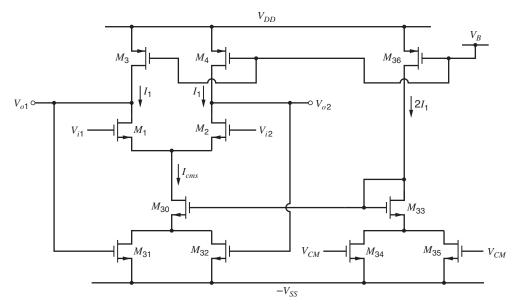

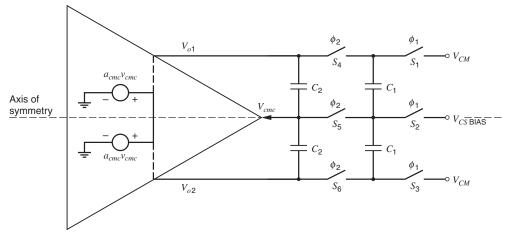

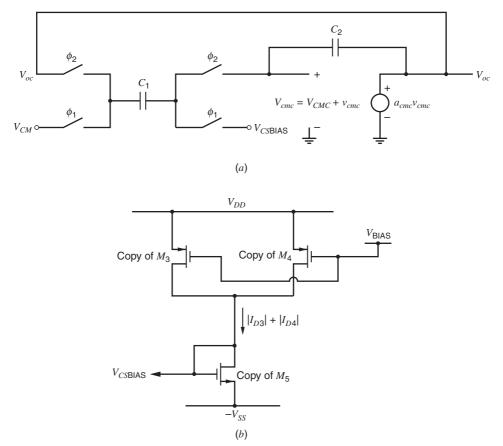

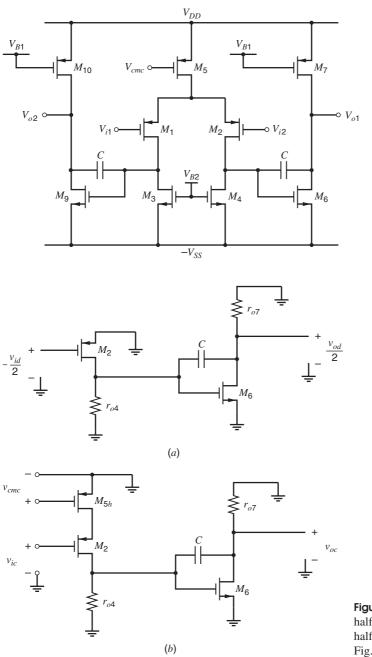

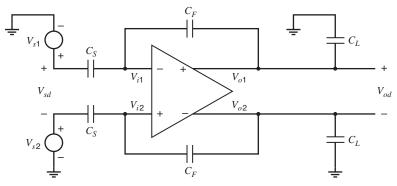

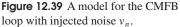

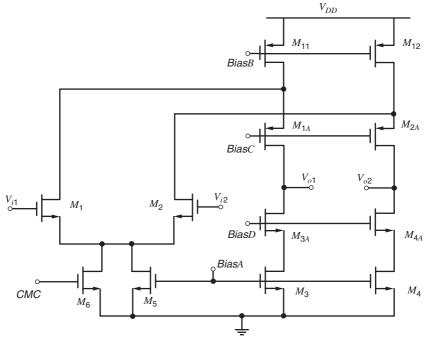

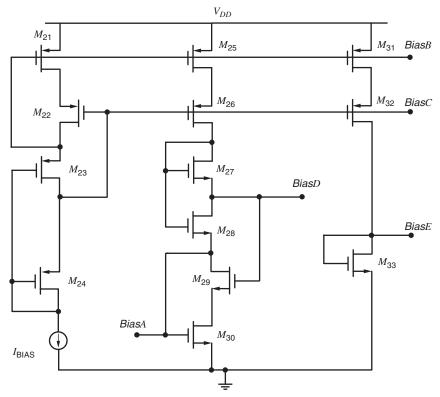

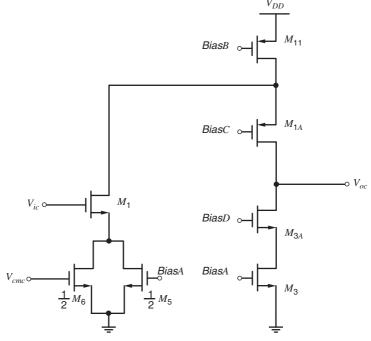

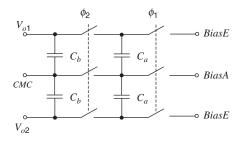

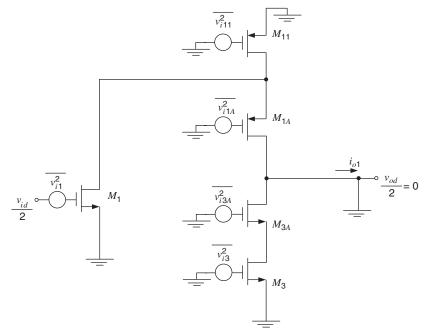

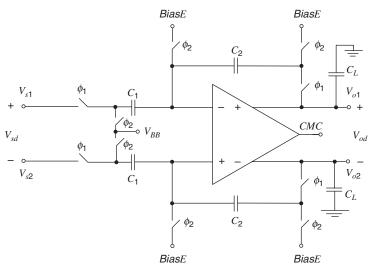

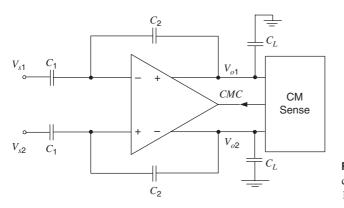

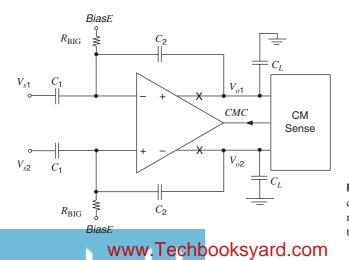

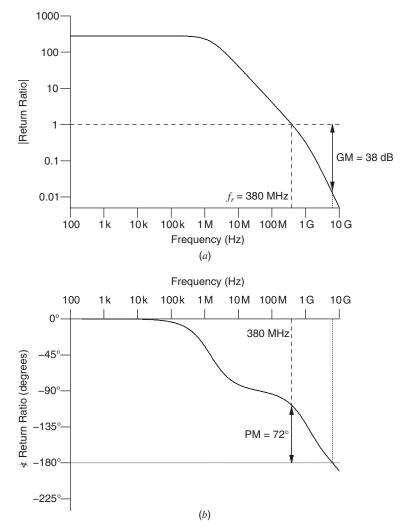

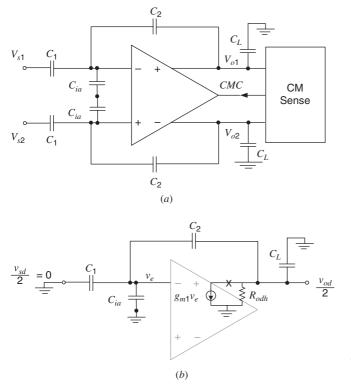

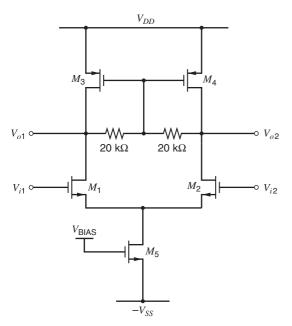

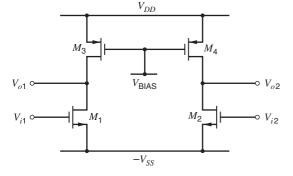

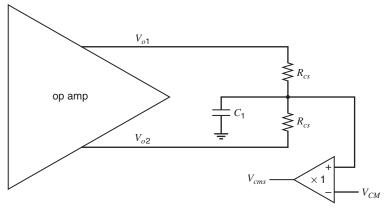

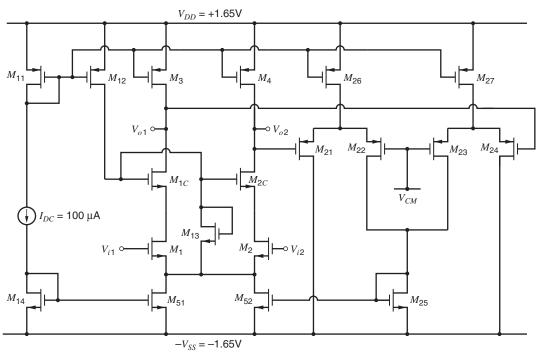

$$I_C = -\alpha_F I_E \frac{1}{1 - \left(\frac{V_{CB}}{BV_{CBO}}\right)^n} \tag{1.75}$$